LSI 53C875A User Manual

Page 137

SCSI Registers

4-45

SDP0L

Latched SCSI Parity

3

This bit reflects the SCSI parity signal (SDP0/),

corresponding to the data latched in the

. It changes when a new byte is latched into

the least significant byte of the SIDL register. This bit is

active HIGH, in other words, it is set when the parity

signal is active.

MSG

SCSI MSG/ Signal

2

C_D

SCSI C_D/ Signal

1

I_O

SCSI I_O/ Signal

0

These three SCSI phase status bits (MSG, C_D, and

I_O) are latched on the asserting edge of SREQ/ when

operating in either the initiator or target mode. These bits

are set when the corresponding signal is active. They are

useful when operating in the low level mode.

1

0

0

1

1

19

1

0

1

0

0

20

1

0

1

0

1

21

1

0

1

1

0

22

1

0

1

1

1

23

1

1

0

0

0

24

1

1

0

0

1

25

1

1

0

1

0

26

1

1

0

1

1

27

1

1

1

0

0

28

1

1

1

0

1

29

1

1

1

1

0

30

1

1

1

1

1

31

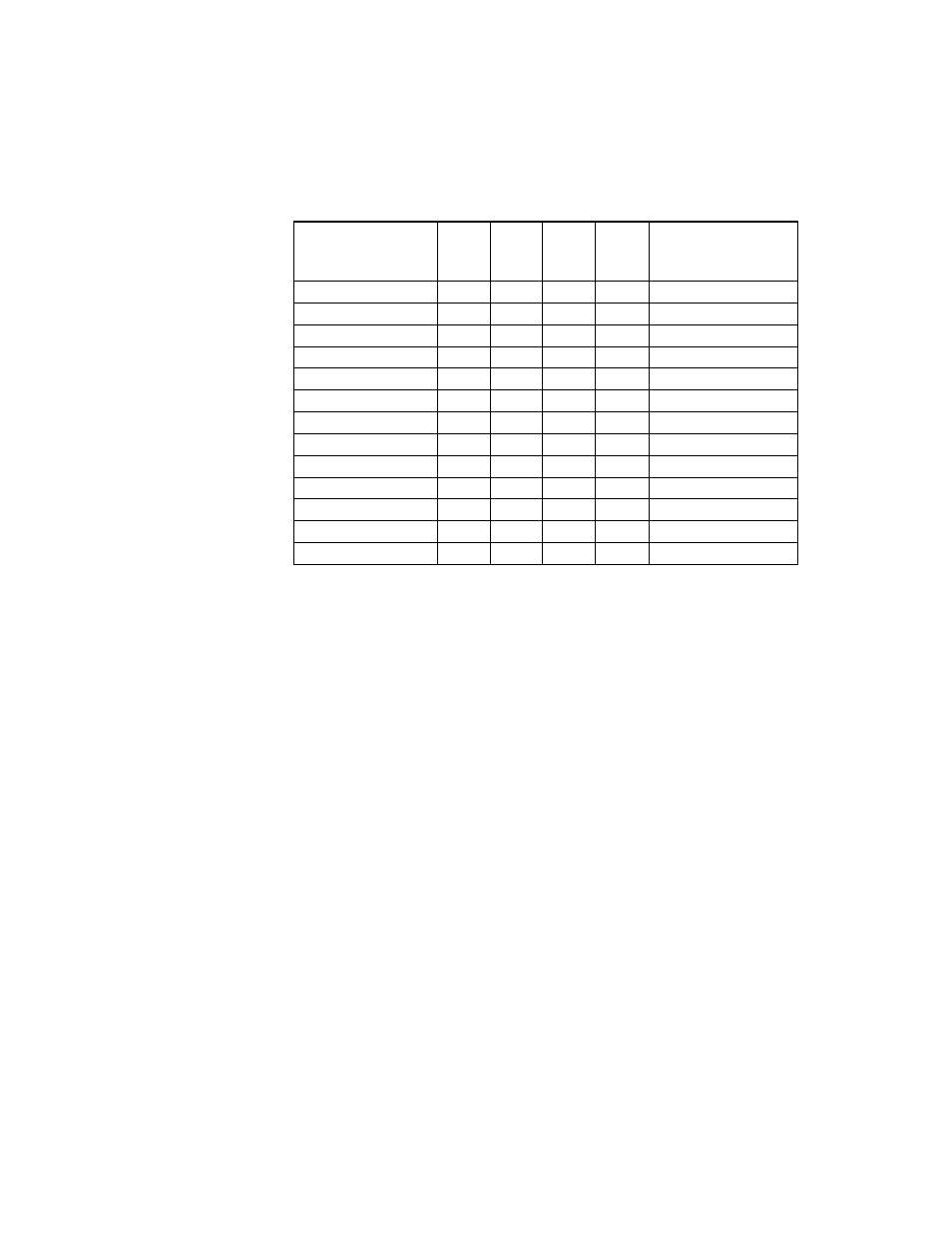

Table 4.6

SCSI Synchronous Data FIFO Word Count (Cont.)

FF4

(SSTAT2 bit 4)

FF3

FF2

FF1

FF0

Bytes or Words

in the

SCSI FIFO