Intel 80L186EA User Manual

Page 13

80C186EA 80C188EA 80L186EA 80L188EA

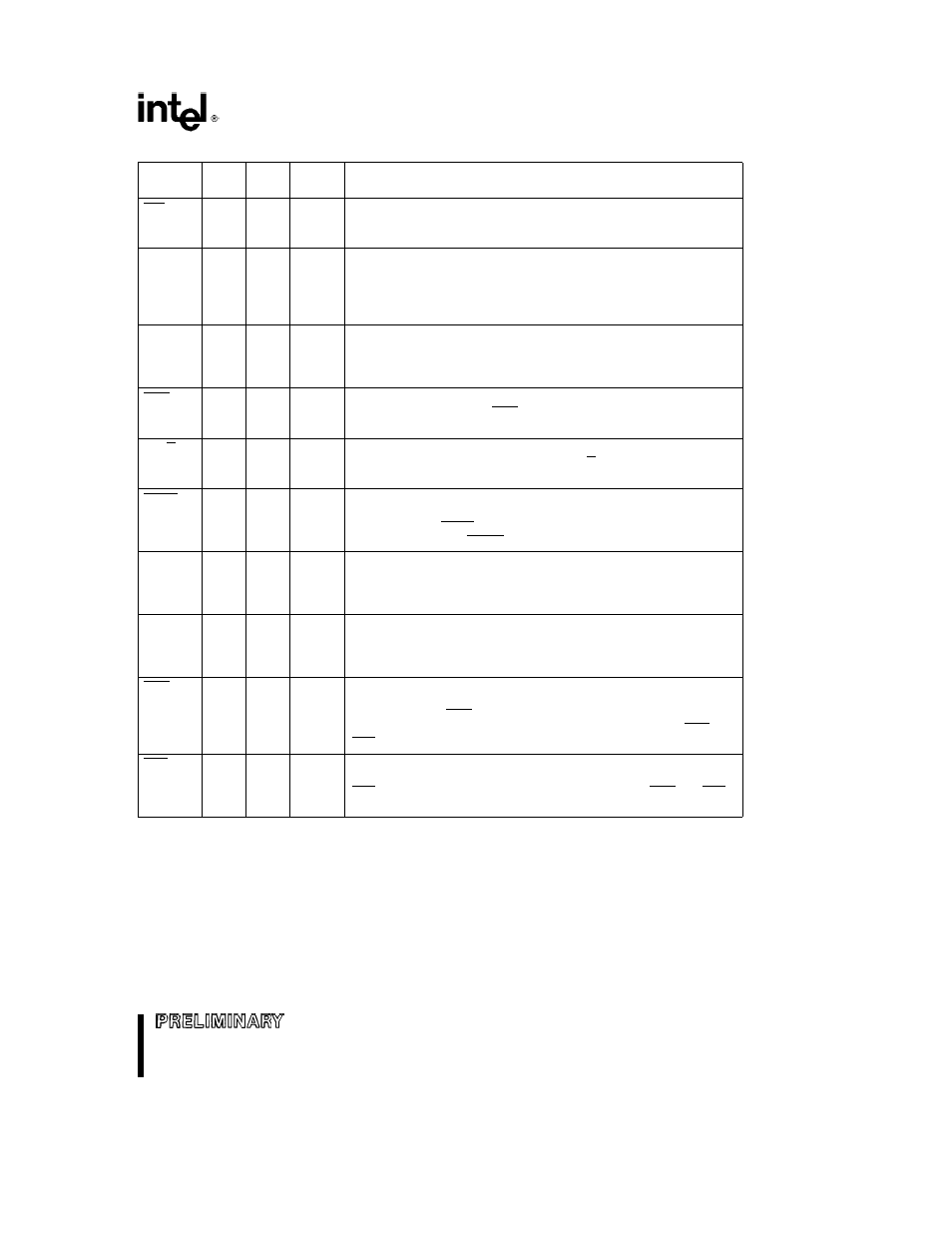

Table 3 Pin Descriptions

(Continued)

Pin

Pin

Input

Output

Description

Name

Type

Type

States

WR QS1

O

H(Z)

WRite

output signals that data available on the data bus are to be

written into the accessed memory or I O device In Queue Status

R(Z)

Mode QS1 provides queue status information along with QS0

P(1)

ARDY

I

A(L)

Asychronous ReaDY

is an input to signal for the end of a bus cycle

ARDY is asynchronous on rising CLKOUT and synchronous on falling

S(L)

CLKOUT ARDY or SRDY must be active to terminate any processor

bus cycle unless they are ignored due to correct programming of the

Chip Select Unit

SRDY

I

S(L)

Synchronous ReaDY

is an input to signal for the end of a bus cycle

ARDY or SRDY must be active to terminate any processor bus cycle

unless they are ignored due to correct programming of the Chip Select

Unit

DEN

O

H(Z)

Data ENable

output to control the enable of bidirectional transceivers

when buffering a system DEN is active only when data is to be

R(Z)

transferred on the bus

P(1)

DT R

O

H(Z)

Data Transmit Receive

output controls the direction of a bi-

directional buffer in a buffered system DT R is only available on the

R(Z)

QFP (EIAJ) package and the SQFP package

P(X)

LOCK

O

H(Z)

LOCK

output indicates that the bus cycle in progress is not to be

interrupted The processor will not service other bus requests (such

R(WH)

as HOLD) while LOCK is active This pin is configured as a weakly

P(1)

held high input while RESIN is active and must not be driven low

HOLD

I

A(L)

HOLD

request input to signal that an external bus master wishes to

gain control of the local bus The processor will relinquish control of

the local bus between instruction boundaries not conditioned by a

LOCK prefix

HLDA

O

H(1)

HoLD Acknowledge

output to indicate that the processor has

relinquished control of the local bus When HLDA is asserted the

R(0)

processor will (or has) floated its data bus and control signals allowing

P(0)

another bus master to drive the signals directly

UCS

O

H(1)

Upper Chip Select

will go active whenever the address of a memory

or I O bus cycle is within the address limitations programmed by the

R(1)

user After reset UCS is configured to be active for memory accesses

P(1)

between 0FFC00H and 0FFFFFH During a processor reset UCS and

LCS are used to enable ONCE Mode

LCS

O

H(1)

Lower Chip Select

will go active whenever the address of a memory

bus cycle is within the address limitations programmed by the user

R(1)

LCS is inactive after a reset During a processor reset UCS and LCS

P(1)

are used to enable ONCE Mode

NOTE

Pin names in parentheses apply to the 80C188EA and 80L188EA

13

13