Intel 80L186EA User Manual

Page 11

80C186EA 80C188EA 80L186EA 80L188EA

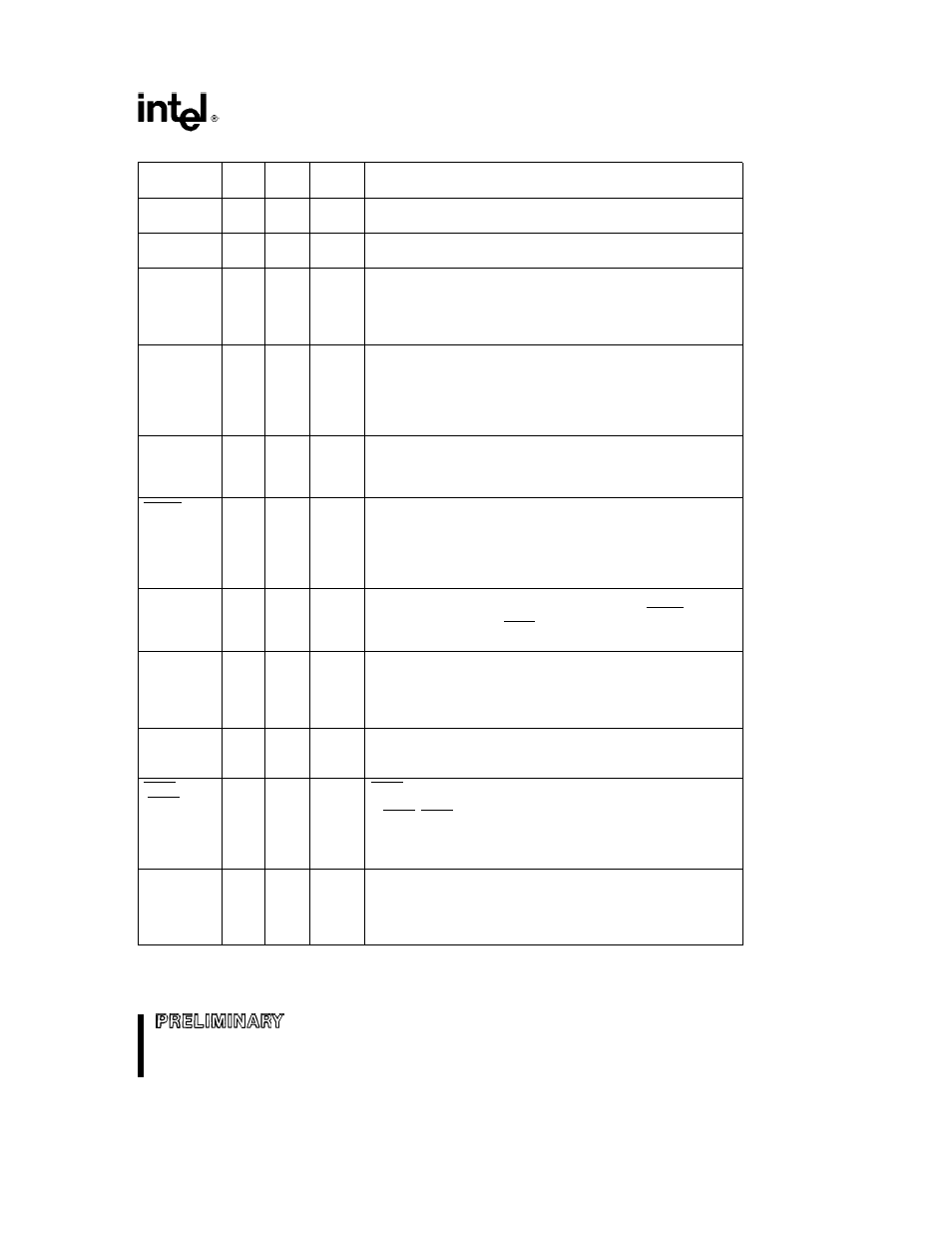

Table 3 Pin Descriptions

Pin

Pin

Input

Output

Description

Name

Type

Type

States

V

CC

P

POWER

connections consist of six pins which must be shorted

externally to a V

CC

board plane

V

SS

G

GROUND

connections consist of five pins which must be shorted

externally to a V

SS

board plane

CLKIN

I

A(E)

CLocK INput

is an input for an external clock An external

oscillator operating at two times the required processor operating

frequency can be connected to CLKIN For crystal operation

CLKIN (along with OSCOUT) are the crystal connections to an

internal Pierce oscillator

OSCOUT

O

H(Q)

OSCillator OUTput

is only used when using a crystal to generate

the external clock OSCOUT (along with CLKIN) are the crystal

R(Q)

connections to an internal Pierce oscillator This pin is not to be

P(Q)

used as 2X clock output for non-crystal applications (i e this pin is

N C for non-crystal applications) OSCOUT does not float in

ONCE mode

CLKOUT

O

H(Q)

CLocK OUTput

provides a timing reference for inputs and outputs

of the processor and is one-half the input clock (CLKIN)

R(Q)

frequency CLKOUT has a 50% duty cycle and transistions every

P(Q)

falling edge of CLKIN

RESIN

I

A(L)

RESet IN

causes the processor to immediately terminate any bus

cycle in progress and assume an initialized state All pins will be

driven to a known state and RESOUT will also be driven active

The rising edge (low-to-high) transition synchronizes CLKOUT with

CLKIN before the processor begins fetching opcodes at memory

location 0FFFF0H

RESOUT

O

H(0)

RESet OUTput

that indicates the processor is currently in the

reset state RESOUT will remain active as long as RESIN remains

R(1)

active When tied to the TEST BUSY pin RESOUT forces the

P(0)

80C186EA into Numerics Mode

PDTMR

I O

A(L)

H(WH)

Power-Down TiMeR

pin (normally connected to an external

capacitor) that determines the amount of time the processor waits

R(Z)

after an exit from power down before resuming normal operation

P(1)

The duration of time required will depend on the startup

characteristics of the crystal oscillator

NMI

I

A(E)

Non-Maskable Interrupt

input causes a Type 2 interrupt to be

serviced by the CPU NMI is latched internally

TEST BUSY

I

A(E)

TEST BUSY

is sampled upon reset to determine whether the

80C186EA is to enter Numerics Mode In regular operation the pin

(TEST)

is TEST TEST is used during the execution of the WAIT

instruction to suspend CPU operation until the pin is sampled

active (low) In Numerics Mode the pin is BUSY BUSY notifies the

80C186EA of 80C187 Numerics Coprocessor activity

AD15 0

I O

S(L)

H(Z)

These pins provide a multiplexed Address and Data bus During

the address phase of the bus cycle address bits 0 through 15 (0

(AD7 0)

R(Z)

through 7 on the 8-bit bus versions) are presented on the bus and

P(X)

can be latched using ALE 8- or 16-bit data information is

transferred during the data phase of the bus cycle

NOTE

Pin names in parentheses apply to the 80C188EA and 80L188EA

11

11