Host bus – HP XU800 User Manual

Page 64

64

2 System Board

Host Bus

Host Bus

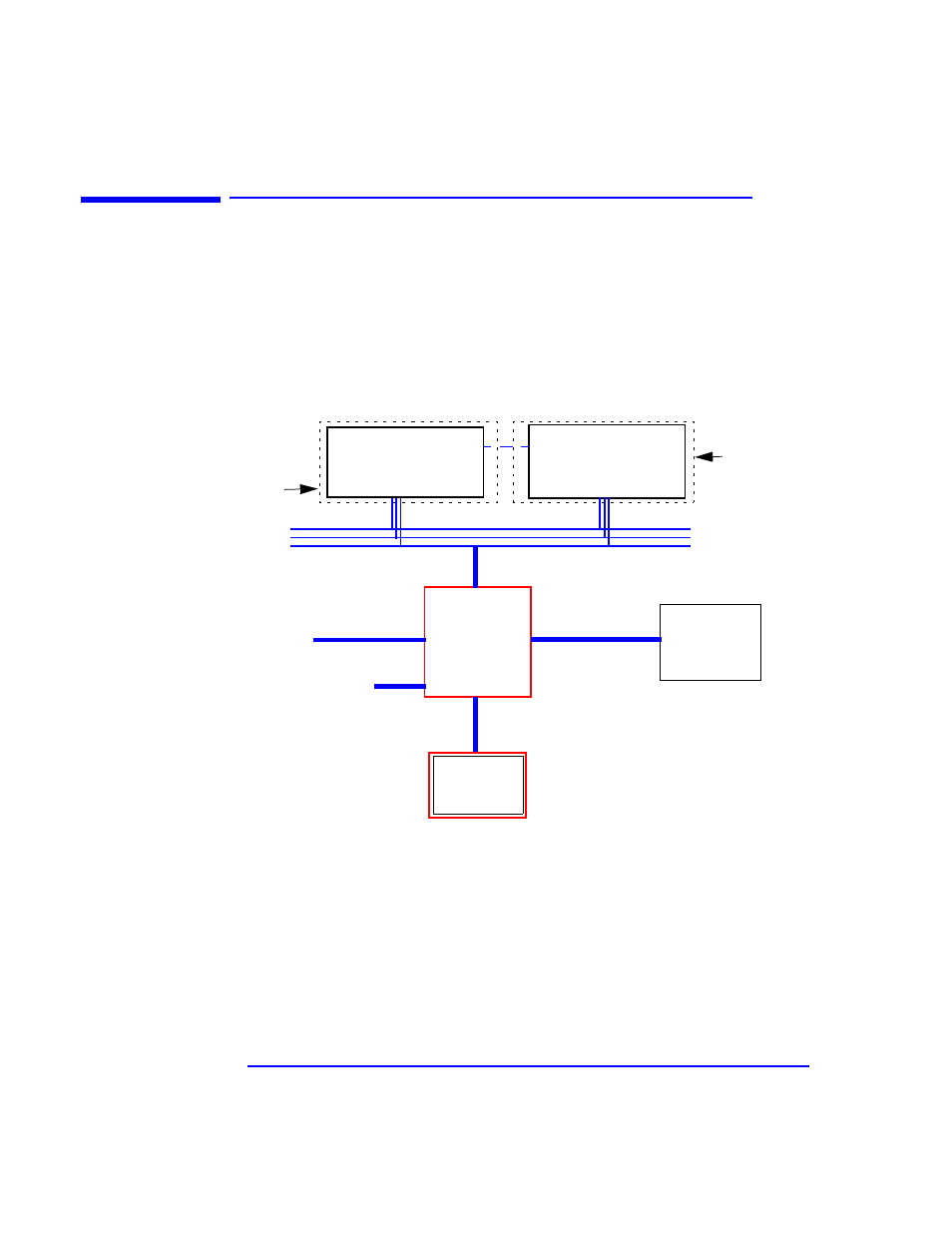

The Host bus of the Pentium III processors, also referred to as the FSB

(Front Side Bus), is implemented in the GTL (Gunning Transceiver Logic)+

technology. This technology features open-drain signal drivers that are

pulled-up to 1.5 V through resistors at bus extremities; these resistors also

act as bus terminators, and are integrated in the processor.

If only one processor is installed, a terminating board must be installed in

the second processor slot.

The supported operating frequencies of the GTL+ bus are 100 MHz or

133 MHz. The width of the data bus is 64 bits, while the width of the address

is 36 bits. Along with the operating frequencies, the processor voltage is set

automatically.

The control signals of the Host bus allow the implementation of a “split -

transaction” bus protocol. This allows the Pentium III processor to send its

request (for example, for the contents of a given memory address) and then

to release the bus, rather than waiting for the result, thereby allowing it to

I840

Memory

Controller Hub

(MCH)

82840-QP

Memory

Expansion Card

Connector

Dual Rambus Bus

Address (36)

Control

Data (64)

AGP

4x Bus

Intel Pentium III

Processor

(optional second processor)

with L2 cache memory

SECC-2 cartridge

SECC-2 cartridge

Host (also called FSB)

Bus 100/133 MHz,

1 GB/sec data trans-

fer rate)

HUB

LINK 16

HUB LINK 8

Intel Pentium III

Processor

with L2 cache memory

I/O Controller

Hub

(ICH) 82801AA