Main memory controller, Dram interface – HP XU800 User Manual

Page 39

39

2 System Board

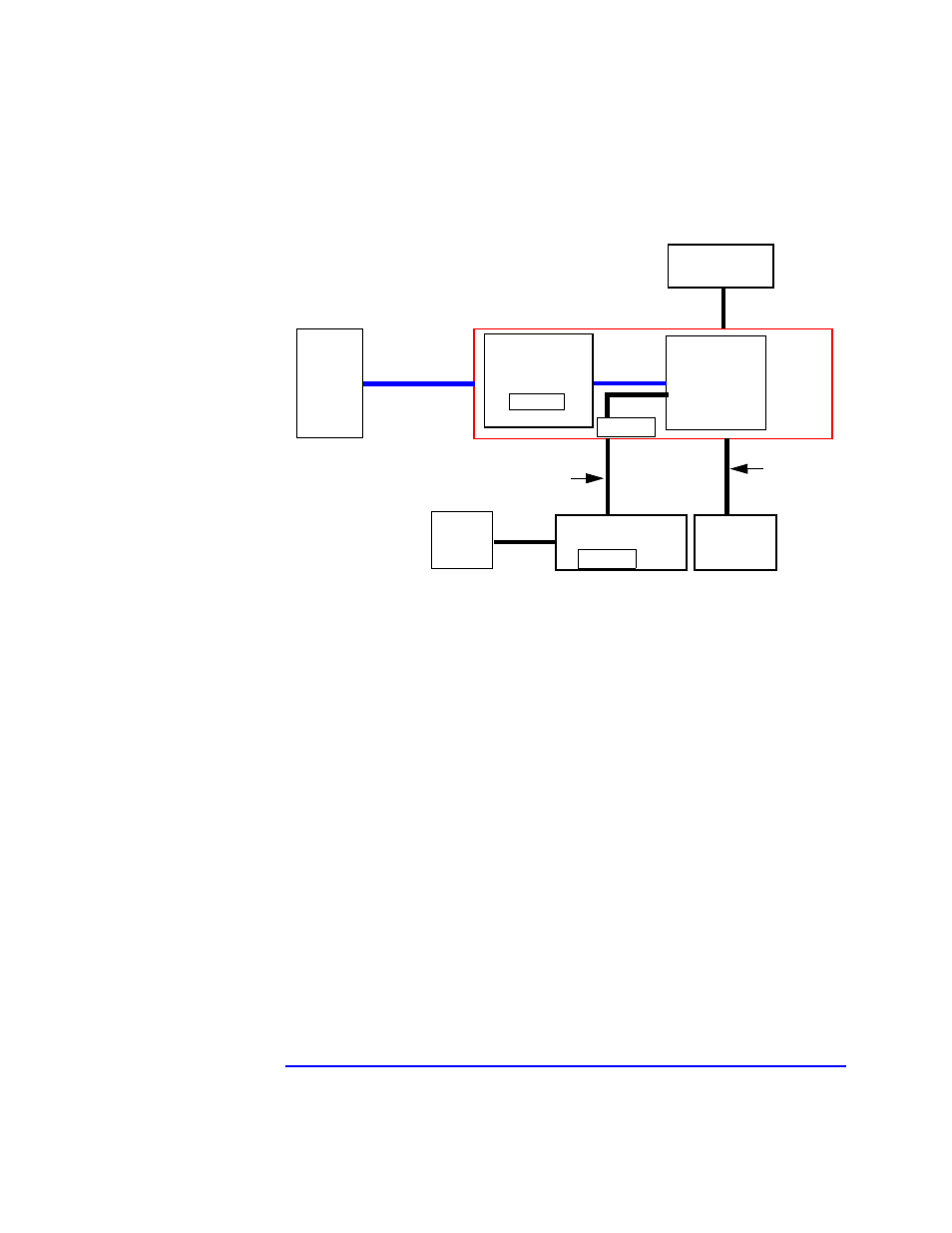

Memory Controller Hub (8240)

AGP PCI Bus

Implementation

Main Memory Controller

The main memory controller is integrated in the MCH supporting two

primary rambus channels (A and B).

DRAM Interface

The MCH provides optional Host bus error checking for data, address,

request and response signals. Only 300 MHz and 400 MHz Direct Rambus

devices are supported in any of 64, 128 or 256 Mb technology. 64 and 128

MBit RDRAMs use page sizes of 1 kbytes, while 256 Mb devices target

1 kbyte or 2 kbyte pages.

A maximum number of 64 Rambus devices (32 devices maximum per

channel) is supported. Both channels must be populated with paired

memory modules.

Pentium III Processor

GX-Device 1

AGP Port

Interface

PCI-to-PCI

Device 0

I840

Memory

Controller Hub

(MCH)

Universal

AGP

PRO

Connector

AGP

4x Bus

(133 MHz)

Hub Link 8-bit

PCI-to-PCI

Two PCI

64-bit 66

MHz slots

PCI 64-bit 66 MHz

Hub (P64H)

I/O Controller

Hub (ICH)

Hub Link 16-bit

PCI-to-PCI

- NRM42 (61 pages)

- ProLiant ML370 (49 pages)

- ProLiant ML370 (50 pages)

- ProLiant ML110 G5 (32 pages)

- PC Comm Station Pro 304251-008 (North America) (5 pages)

- 100B-TX (32 pages)

- 3C905B-TX (110 pages)

- EK-STWCT-UG. E01 (45 pages)

- 3800ux (13 pages)

- 5991-6764 (8 pages)

- LTO 4 FC (46 pages)

- StorageWorks Network Attached Storage X3000 (16 pages)

- Ultrium Drive (30 pages)

- ProLiant DL360 (49 pages)

- CD Leycom CFL-512 (5 pages)

- RDX160 (12 pages)

- 345524-B21 (54 pages)

- DT-20 (20 pages)

- SureStore 7115w (136 pages)

- HD1600 (2 pages)

- ProLiant DL160 (38 pages)

- Vectra XW (16 pages)

- D2D4004i (20 pages)

- F1588A (4 pages)

- 94500 (1 page)

- Computer Parts (21 pages)

- MSA50 (8 pages)

- 7750 (32 pages)

- Media Gateways G350 (76 pages)

- P400 Serial (9 pages)

- MSL4048 (4 pages)

- 3C590-TPO (40 pages)

- mv2040 (2 pages)

- AHA-8940 (82 pages)

- ProLiant DL385 (47 pages)

- ProLiant DL385 (174 pages)

- 5300A (19 pages)

- AMD Geode E2047551001R (111 pages)

- 1100d (102 pages)

- Reliable Transaction Router (100 pages)

- xp1024 (2 pages)

- 180 Degree Turn (24 pages)

- procurve J8165A (32 pages)

- 04H8095 (28 pages)

- 744 (154 pages)