Memory controller hub (8240) – HP XU800 User Manual

Page 35

35

2 System Board

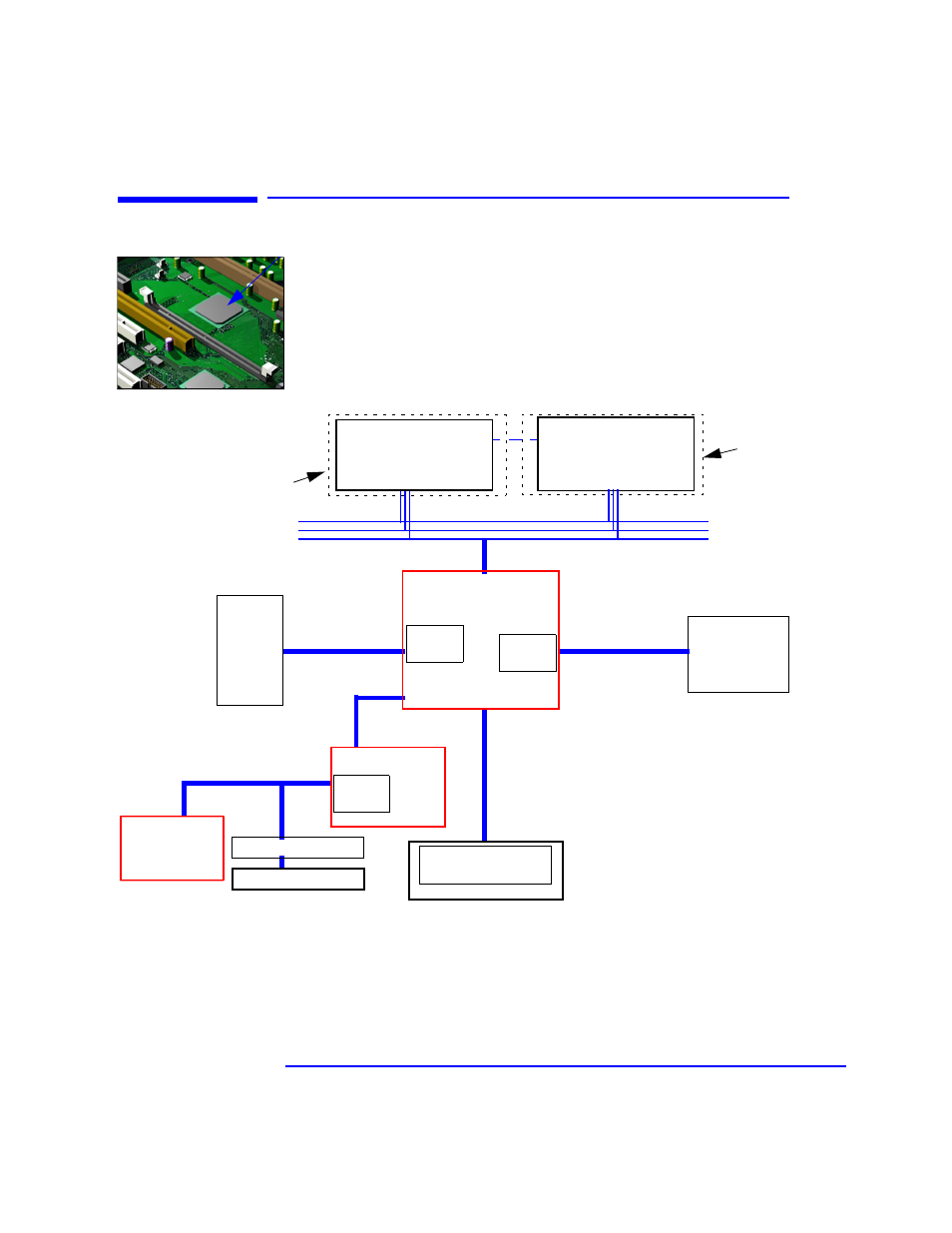

Memory Controller Hub (8240)

Memory Controller Hub (8240)

The MCH Host Bridge/Controller is contained in a 544-pin Ball Grid Array

(BGA) package and is the bridge between the Host bus, Dual Rambus bus

(main memory), AGP 4x (graphic) bus, Hub Link 8-bit and Hub Link

16-bit.

The following figure shows an example of the system block diagram using

the MCH.

I840 Memory

Controller Hub (MCH)

82840-QP

Memory

Expansion Card

Connector

PCI Bus (64-bit, 66 MHz)

533 MB/s data transfer rate

Dual Rambus Bus

Address (36)

Control

Data (64)

AGP

4x Bus

(133 MHz (1 GB MB/s

data transfer rate)

Intel Pentium III

Processor

(optional second processor)

with L2 cache memory

SECC-2 cartridge

(533 MB/s data

transfer rate)

P64H

Onboard AIC7892

SCSI U160

Controller

HUB

LINK 16

HUB LINK 8

(266 MB/s data

transfer rate)

Slot 4 - 64-bit/66 MHz

Slot 3 - 64-bit/66 MHz

Intel Pentium III

Processor

with L2 cache memory

I/O Controller Hub

(ICH) 82801AA

(2.4 GB/s at 300 MHz or

3.2 GB/s at 400 MHz-

data transfer rate)

SECC-2 cartridge

AGP

Interface

PCI

Interface

Memory

Controller

Universal

AGP

PRO

Connector

Host (also called FSB) Bus

100/133 MHz, 1 GB/sec

data transfer rate)