Decimator register – 0x1e – Sundance SMT384 User Manual

Page 35

Version 1.4

Page 35 of 47

SMT384 User Manual

1

01

ADC Channel C only ; 2 samples packed onto one 32-bit word [word(t+1) word(t)]

2

10

ADC Channel D only ; 2 samples packed onto one 32-bit word [word(t+1) word(t)]

3

11

ADC Channel C and D ; 1 sample of each ADC channel packed onto one 32-bit word. [ChD ChC]

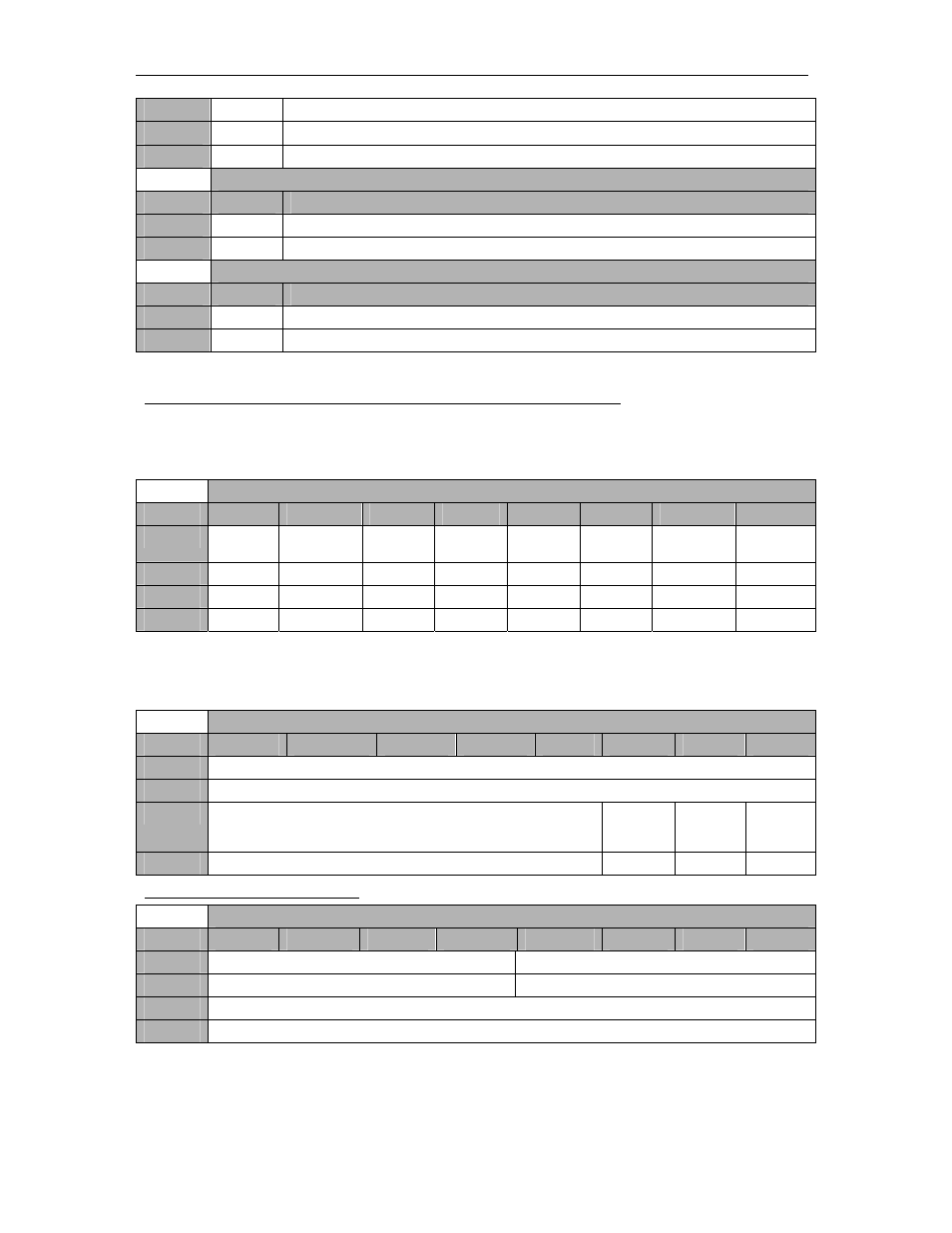

Miscellaneous Register – 0x1C

Setting

Bit 12

Description – ADC A and B Data Format

0

0

ADC A and B output binary samples

1

1

ADC A and B output 2’s complement samples

Miscellaneous Register – 0x1C

Setting

Bit 13

Description – ADC C and D Data Format

0

0

ADC C and D output binary samples

1

1

ADC C and D output 2’s complement samples

Updates, Read-back and Firmware Version Registers – 0x1D

The Update bit activates the corresponding Serial Interface to pass registers

previously written in the FPGA, into the corresponding device (ADCA, ADCB, ADCC,

ADCD or CLK devices).

Update and Read-back commands – 0x1D

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved Reserved Reserved Reserved CLK

Update

Reserved ADCC&D

Update

ADCA&B

Update

Default

‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’

1

Reserved

Reserved

Default

‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’

Reading-back this register returns the Firmware version as well as some Status

signals coming from theAD9510.

Firmware Version – 0x1D

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Firmware Version

Default

‘00000000’

1

Reserved AD9510

Status

Lock

AD9510

Status

Ref

AD9510

Status

VCXO

Default

‘00000’ ‘0’

‘0’

‘0’

Decimator Register – 0x1E.

Decimator Register – 0x1E

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Decimation Factor ADC ChannelC&D

Decimation Factor ADC ChannelA&B

Default

‘0000’ ‘0000’

1

Reserved

Default

‘00000000’