Register descriptions reset register – 0x0 – Sundance SMT384 User Manual

Page 27

Version 1.4

Page 27 of 47

SMT384 User Manual

0x3B

AD9510 Register 0xB.

Read-back (FPGA Register) AD9510 Register B.

0x3C

AD9510 Register 0xC.

Read-back (FPGA Register) AD9510 Register C.

0x3D

AD9510 Register 0xD.

Read-back (FPGA Register) AD9510 Register D.

0x3E

AD9510 Register 0xE.

Read-back (FPGA Register) AD9510 Register E.

0x3F

AD9510 Register 0xF.

Read-back (FPGA Register) AD9510 Register F.

0x40

AD9510 Register 0x10.

Read-back (FPGA Register) AD9510 Register 10.

0x41

AD9510 Register 0x11.

Read-back (FPGA Register) AD9510 Register 11.

0x42

AD9510 Register 0x12.

Read-back (FPGA Register) AD9510 Register 12.

0x43

AD9510 Register 0x13.

Read-back (FPGA Register) AD9510 Register 13.

0x44

AD9510 Register 0x14.

Read-back (FPGA Register) AD9510 Register 14.

0x45

AD9510 Register 0x15.

Read-back (FPGA Register) AD9510 Register 15.

0x46

AD9510 Register 0x16.

Read-back (FPGA Register) AD9510 Register 16.

0x47

AD9510 Register 0x17.

Read-back (FPGA Register) AD9510 Register 17.

0x48

AD9510 Register 0x18.

Read-back (FPGA Register) AD9510 Register 18.

0x49

AD9510 Register 0x19.

Read-back (FPGA Register) AD9510 Register 19.

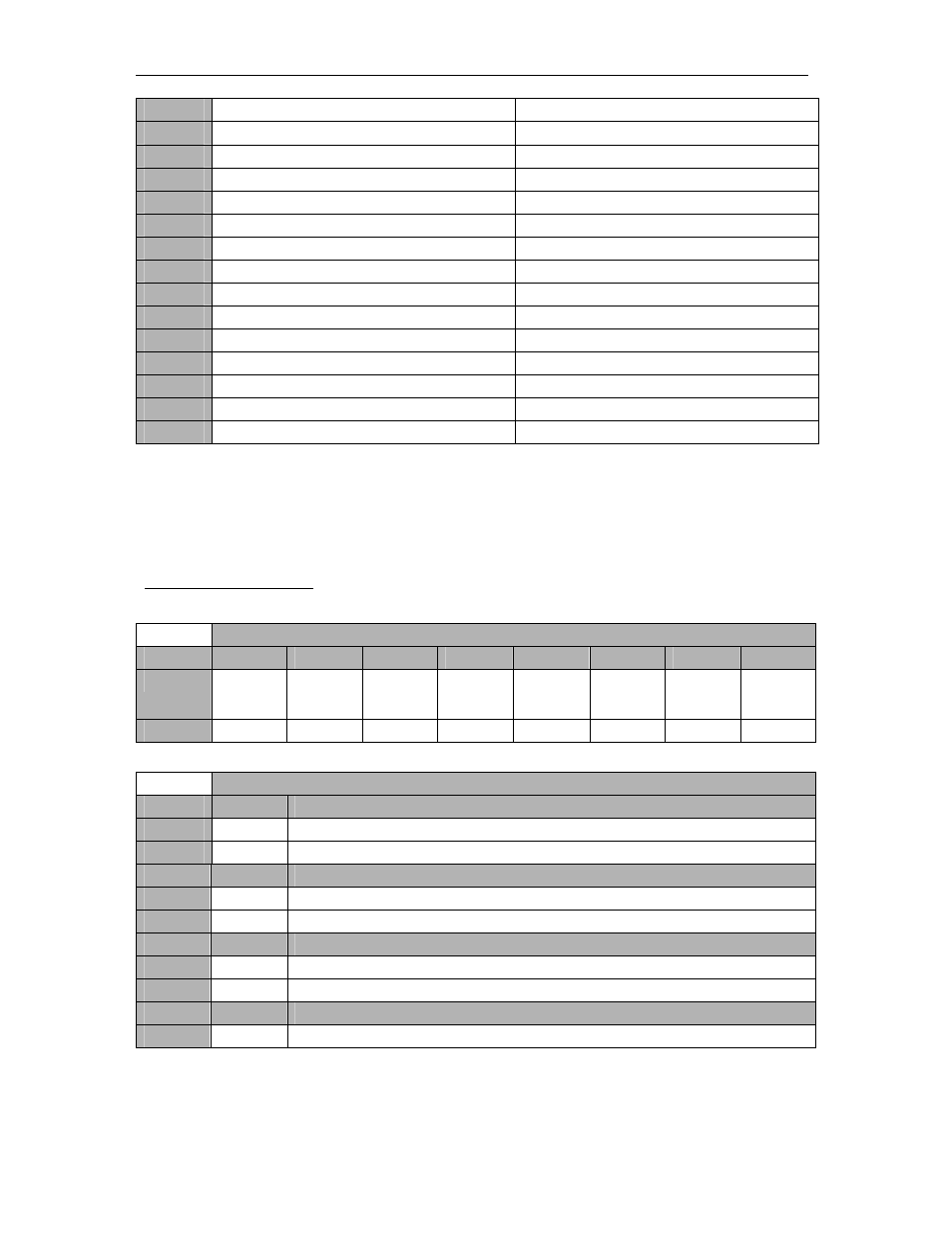

Figure 16 – Register Memory Map.

Register Descriptions

Reset Register – 0x0.

Reset Register – 0x0

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

SHB ChC

and D

Reset

SHB ChA

and B

Reset

Reserved Reserved Reserved AD9510

Reset

ADC C&D

Reset

ADC A&B

Reset

Default

‘1’ ‘1’ ‘0’ ‘0’ ‘0’ ‘1’ ‘1’ ‘1’

Reset Register – 0x0

Setting

Bit 0

Description – ADC A&B Reset

0

0 Normal

Operation.

1

1

Resets both ADC devices as well as their corresponding Serial Interfaces.

Setting

Bit 1

Description – ADC C&D Reset

0

0 Normal

Operation.

1

1

Resets both ADC devices as well as their corresponding Serial Interfaces.

Setting

Bit 2

Description – AD9510 Reset

0

0 Normal

Operation.

1

1

Resets Clock device as well as its Serial Interfaces.

Setting

Bit 6

Description – SHB ADC A&B Reset

0

0 Normal

Operation.