Bank a bank b bank c, Bank a (adc a and b) – Sundance SMT384 User Manual

Page 21

Version 1.4

Page 21 of 47

SMT384 User Manual

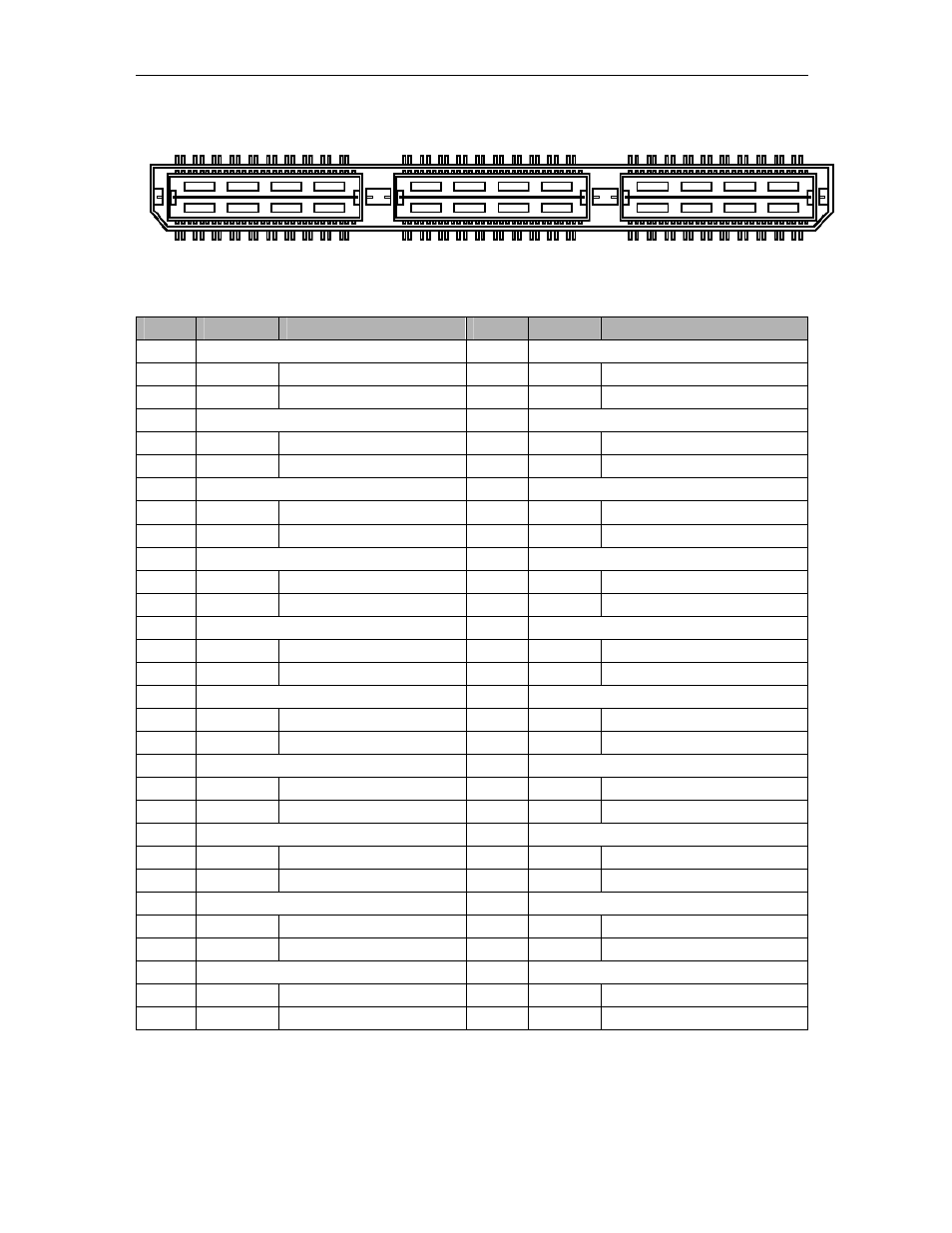

Bank

A Bank

B Bank

C

1 3 5 7

41 43

81 83

2 4 6 8

Bank A (ADC A and B)

Pin No

Pin Name

Signal Description

Pin No

Pin Name

Signal Description

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

1

DOAI0p

Data Out 0, Channel A.

2

DOBI0p

Data Out 1, Channel A.

3

DOAI0n

Data Out 2, Channel A.

4

DOBI0n

Data Out 3, Channel A.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

5

DOAI1p

Data Out 4, Channel A.

6

DOBI1p

Data Out 5, Channel A.

7

DOAI1n

Data Out 6, Channel A.

8

DOBI1n

Data Out 7, Channel A.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

9

DOAI2p

Data Out 8, Channel A.

10

DOBI2p

Data Out 9, Channel A.

11

DOAI2n

Data Out 10, Channel A.

12

DOBI2n

Data Out 11, Channel A.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

13

DOAI3p

Data Out 12, Channel A.

14

DOBI3p

Data Out 13, Channel A.

15

DOAI3n

Over Range, Channel A.

16

DOBI3n

Data Out 0, Channel B.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

17

DOAI4p

Data Out 1, Channel B.

18

DOBI4p

Data Out 2, Channel B.

19

DOAI4n

Data Out 3, Channel B.

20

DOBI4n

Data Out 4, Channel B.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

21

DOAI5p

Data Out 5, Channel B.

22

DOBI5p

Data Out 6, Channel B.

23

DOAI5n

Data Out 7, Channel B.

24

DOBI5n

Data Out 8, Channel B.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

25

DOAI6p

Data Out 9, Channel B.

26

DOBI6p

Data Out 10, Channel B.

27

DOAI6n

Data Out 11, Channel B.

28

DOBI6n

Data Out 12, Channel B.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

29

DOAI7p

Data Out 13, Channel B.

30

DOBI7p

Over Range, Channel B.

31

DOAI7n

Led ADC A and B.

32

DOBI7n

Status Lock AD9510

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

33

ClkOIp

Data Clock Out, Channel A.

34

DOIRIp

Status Ref AD9510

35

ClkOIn

Data Clock Out, Channel B.

36

DOIRIn

Status VCXO AD9510

Dir Reserved.

Dir Reserved.

37

Reserved.

Reserved.

38

Reserved

ADC A and B External Trigger, P.

39

Reserved.

Reserved.

40

Reserved

ADC A and B External Trigger, N.

Figure 11 – Daughter Module Interface: Data Signals Connector and Pinout (Bank A).