Sundance SMT384 User Manual

Page 16

Version 1.4

Page 16 of 47

SMT384 User Manual

ADCs can all receive the same clock or the integer multiple of it (x2, x3, …x32), the

maximum being 125MHz for each ADC. This clock can be coming from the on-board

VCXO or from an external source.

An extra connector outputs the reference clock for multiple-module systems.

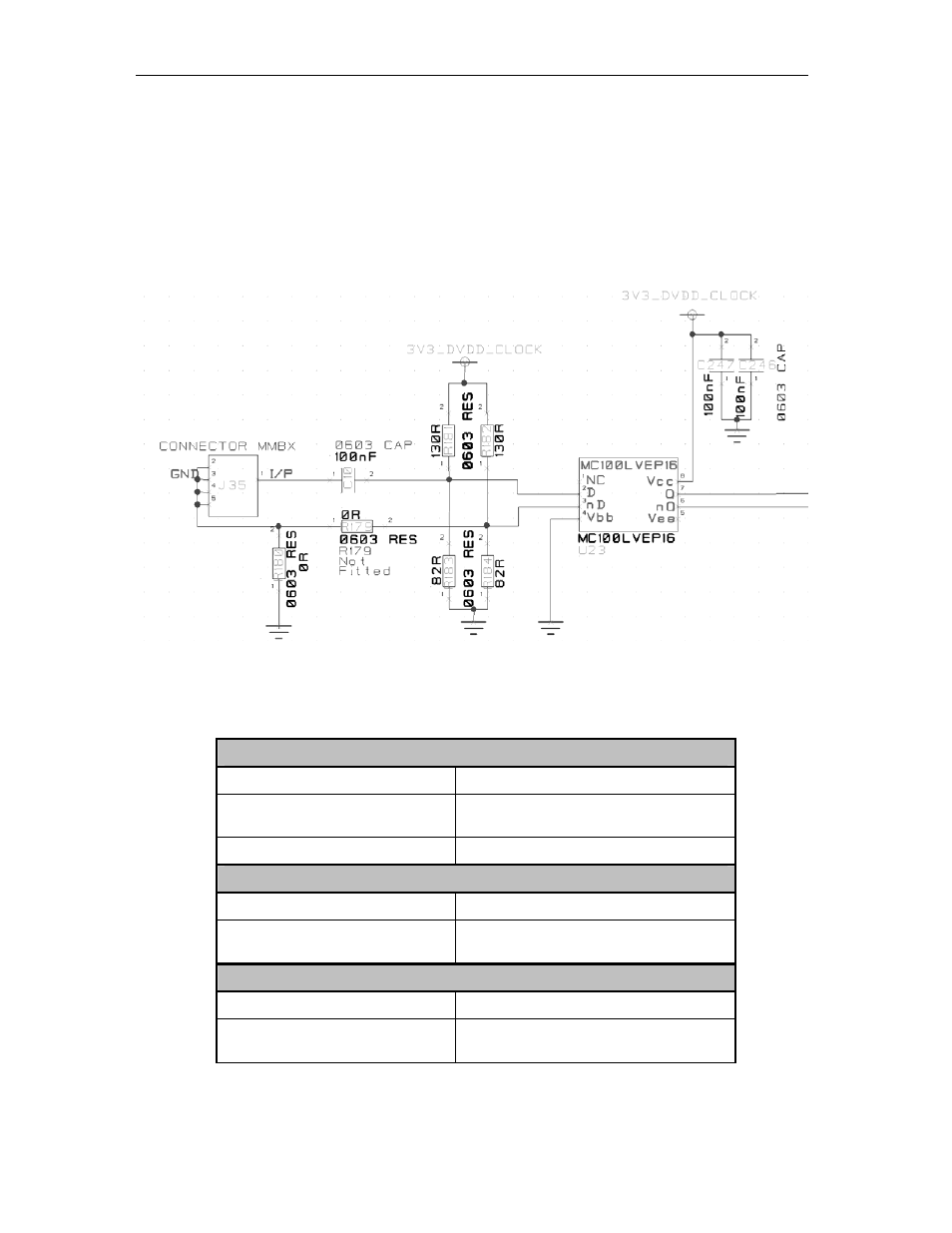

Below is shown how the external clock is fed to the system. By default it is single-

ended and AC-coupled before being converted into LVPECL format. The option of

having a differential external clock is still possible on the hardware by the way of

fitting or not some of the components.

Figure 7 - External Clock.

The main characteristics of the SMT384 Clocks are gathered into the following table.

External Reference Input

Input Voltage Level

0.5 – 3.3 Volts peak-to-peak (AC-coupled)

Input Impedance

50-Ohm (Termination implemented at the

connector)

Frequency Range

0 – 100 MHz.

External Reference Output

Output Voltage Level

1.6 Volts peak-to-peak (AC-coupled)

Output Impedance

50-Ohm (Termination implemented at the

connector)

External Sampling Clock Input

Input Voltage Level

0.5 – 3.3 Volts peak-to-peak (AC-coupled)

Format

Single-ended or differential on option (3.3V

LVPECL).