9 base + 11 - reserved register, 10 pacer clock data & control registers – Measurement Computing CIO-DAS16 User Manual

Page 28

When TRIG0 = 0, the external trigger at pin 25 has no effect on the GATEs of counter 1 and 2.

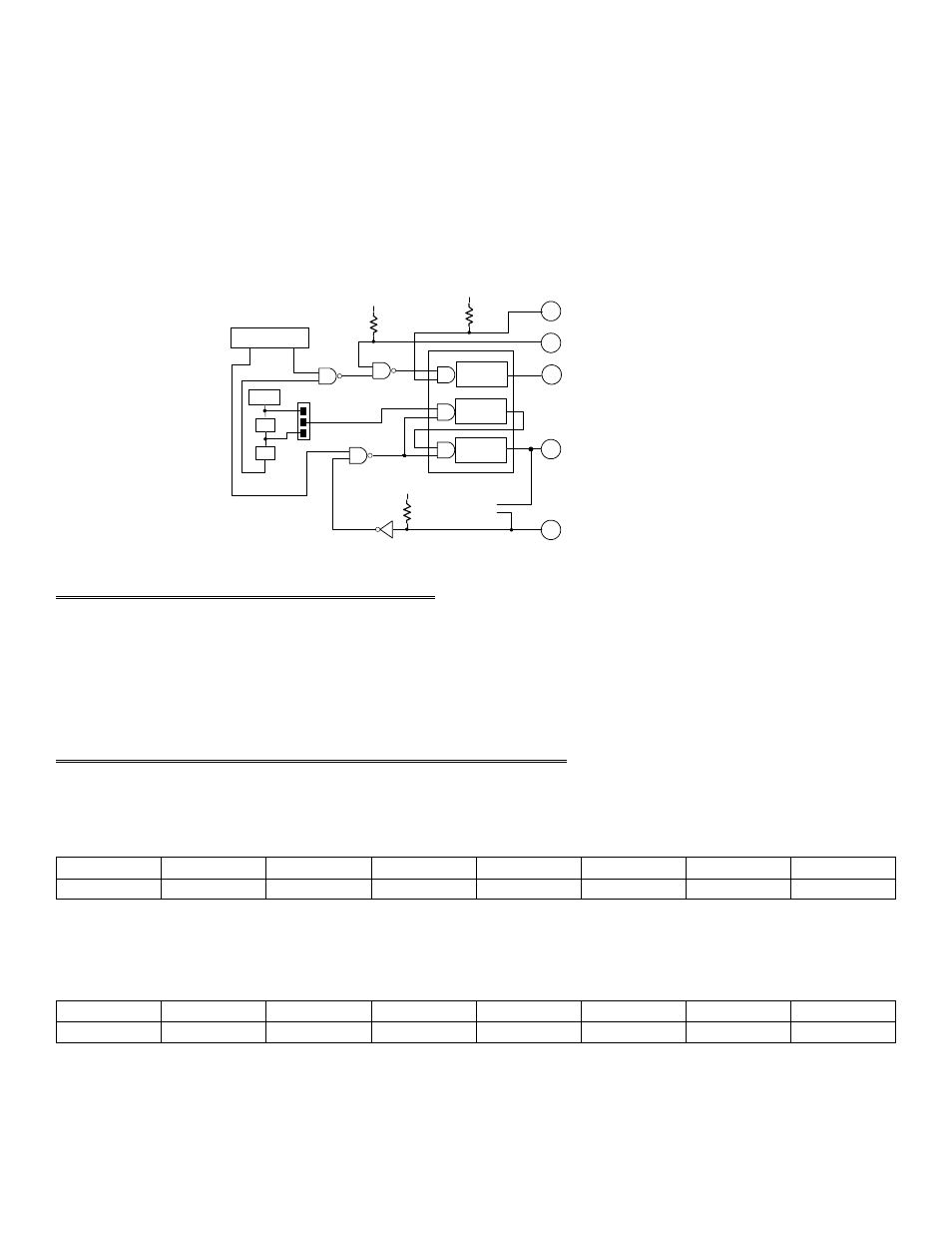

See Figure 4-1 for a block diagram of the Pacer Clock logic.

Figure 4-1. Pacer Clock and Control Logic

4.9 BASE + 11 - RESERVED REGISTER

BASE ADDRESS + 11

This address is reserved for use as a programmable gain register in other DAS16 family boards.

4.10 PACER CLOCK DATA & CONTROL REGISTERS

8254 COUNTER 0 DATA

BASE ADDRESS +12

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

8254 COUNTER 1 DATA

BASE ADDRESS +13

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

24

10 MHz

2

COUNTER 0

20

COUNTER 2

COUNTER 1

A/D PACER

25

24

+5V

10K

21

+5V

10K

1 /10

1 /10

CONTROL REGISTER

BASE + 10

CTR0

GATE

GATE

GATE

OUT

OUT

OUT

10 MHz

1MHz

+5V

10K

CTR 2 OUT

CTR 0 OUT

TRIGGER

TRIG0

CTR 0 GATE

CTR 0 CLOCK IN

This manual is related to the following products: