Aggregate data/clock input, power connector, Mode and sync connector, Secondary demodulator interface connector – Comtech EF Data SDR-54A User Manual

Page 77: 4 aggregate data/clock input, power connector, 5 mode and sync connector, 6 secondary demodulator interface connector

SDR-54A Satellite Demodulator

Revision 4

Specifications

MN/SDR54A.IOM

8.12.4

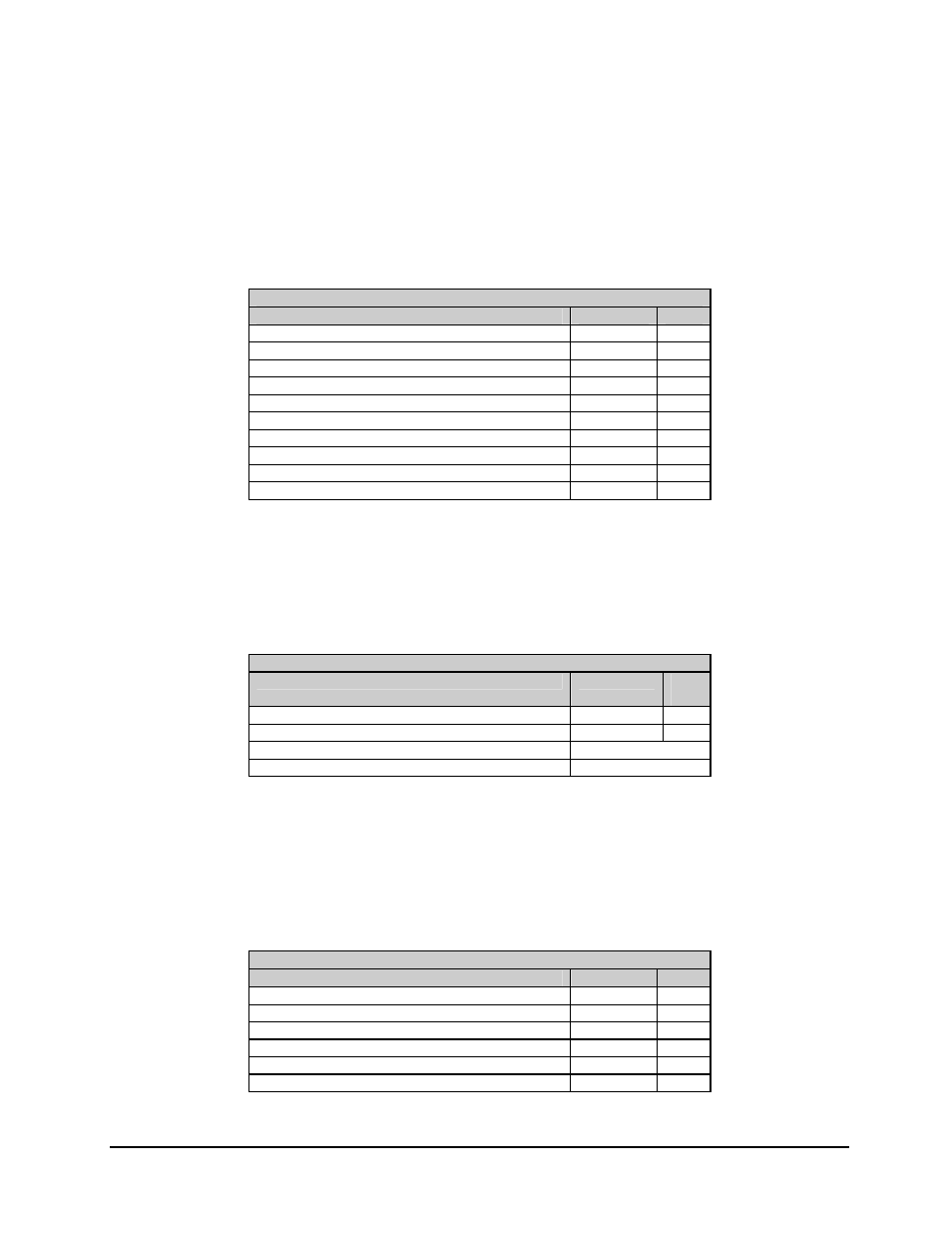

Aggregate Data/Clock Input, Power Connector

Connector type: Dual row (2 x 5), Female.

Table 8-13. Aggregate Data/Clock Input, Power Connector

Aggregate Data/Clock Input, Power Connector

Signal Function

Name

Pin #

Aggregate Data - Inverted

/ADAT

1

Barker Word Data Sequence

BARK

2

IIC Serial Control Data

SDA

3

Barker Word Sequence Timing Pulse

BARKNOT

4

IIC Serial Control Clock

SCL

5

Spare BARK3

6

Aggregate Clock Non-Inverted

ACLK

7

+5 VDC

+5VDC

8

+5 VDC

+5VDC

9

Ground GND

10

8.12.5

Mode and Sync Connector

Connector type

:

Dual row (2 x 13), Female.

Table 8-14. Mode and SYNC Connector (JP2)

Mode and Sync Connector JP2

Signal Function

Name

Pin

#

Demux synchronization indicator (TTL, 1 = SYNC)

DMXSYNC

6

Demux mode indicator

DMXMD

9

Ground GND

13, 26

No Connects

1-5, 7, 8, 10-25

8.12.6

Secondary Demodulator Interface Connector

Connector type

:

Dual row (2 x 5), Female.

Table 8-15. Secondary Demodulator Interfacve Connector

Secondary Demodulator Interface Connector

Signal Function

Name

Pin #

Xilinx CCLK from Main Board

CCLK

1

Xilinx DOUT from Main Board

DOUT

2

Spare DMSPR_1

3

Spare DMSPR_2

4

No Connect

NC

5 to 9

Ground GND

10

8–17