Carrier and clock acquisition time, Received if carrier acquisition range, Received data clock frequency error – Comtech EF Data SDR-54A User Manual

Page 67: 3 carrier and clock acquisition time, 1 received if carrier acquisition range, 2 received data clock frequency error

SDR-54A Satellite Demodulator

Revision 4

Specifications

MN/SDR54A.IOM

8.3

Carrier and Clock Acquisition Time

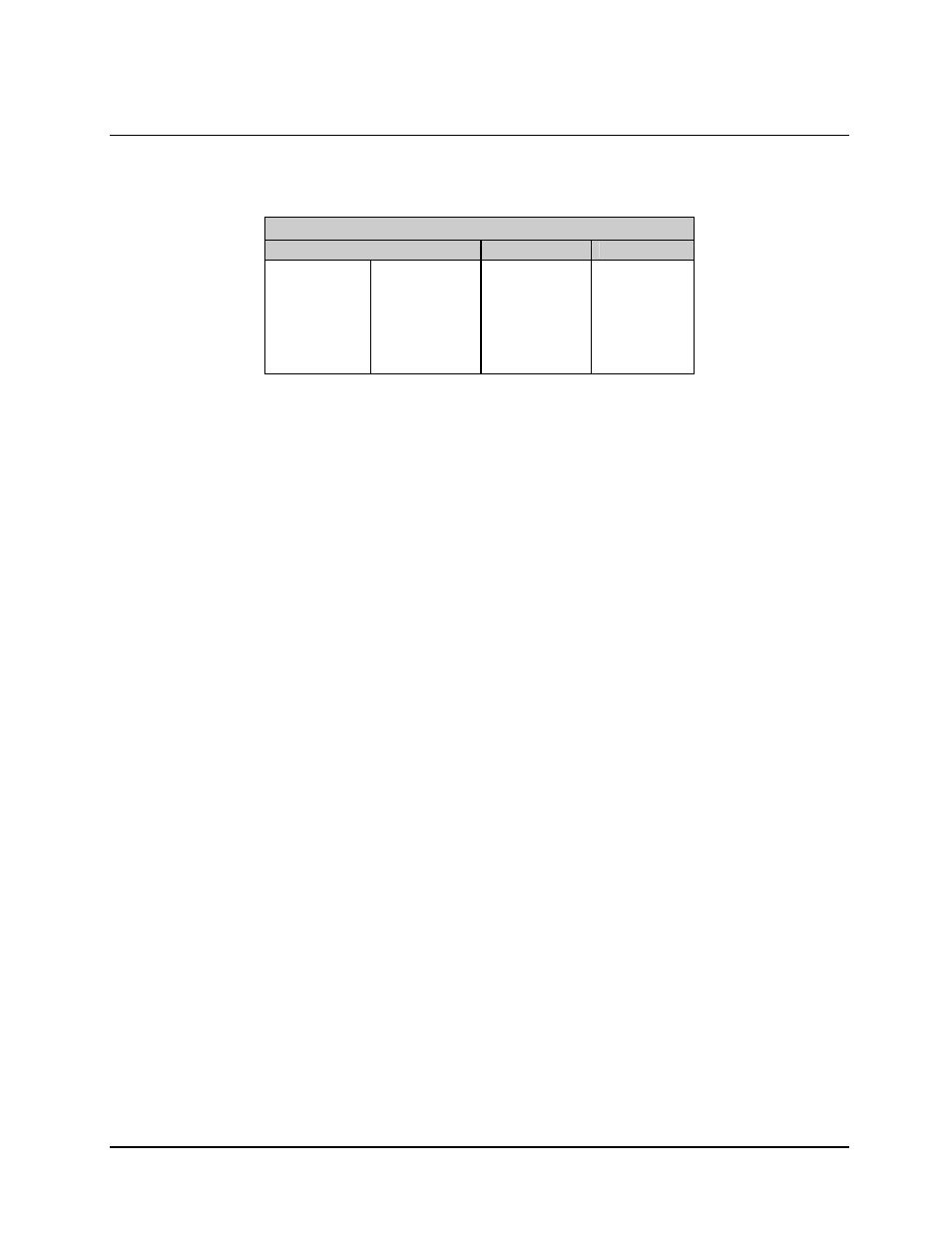

Table 8-7. Carrier and Clock Acquisition Time

Viterbi

Symbol Rate Range

BPSK Time

QPSK Time

512K

≤

R

s

< 2500K

≤ 2.55 sec

≤ 2.55 sec

178K

≤

R

s

< 512K

≤ 20.0 sec

≤ 10.0 sec

70K

≤

R

s

< 178

≤ 5 sec

≤ 10 sec

40K

≤

R

s

< 70K

≤ 25 sec

≤ 50 sec

19.2K

≤

R

s

< 40K

≤ 55 sec

≤ 1100 sec

R

s

< 19.2K

< 110 sec

< 220 sec

The receiver will acquire carrier and data clock synchronization from continuous

transmissions only from a randomly modulated portion of the received transmission

(i.e., without preamble) with a probability of success of greater than 95% per Table 8-7.

The above probability of success is met under the following worst case conditions:

• The input Eb/N0 is no less than 6.0 dB for 1/2 rate coding, 7.4 dB for 3/4 rate, and

8.5 dB for 7/8 rate.

• Carrier frequency uncertainty of ± 30 kHz.

• Data clock frequency error of ± 100 PPM.

8.3.1

Received IF Carrier Acquisition Range

The acquisition range of the demodulator is programmed from 10.0 kHz to 1 MHz,

in steps of 10 kHz.

8.3.2

Received Data Clock Frequency Error

The data clock frequency error of the signal applied to the demodulator input must not

exceed

± 100 PPM.

8–7