Demux 8-channel specification, 3 demux 8-channel specification – Comtech EF Data SDR-54A User Manual

Page 44

SDR-54A Satellite Demodulator

Revision 4

DEMUX Option

MN/SDR54A.IOM

5.3.3

DEMUX 8-Channel Specification

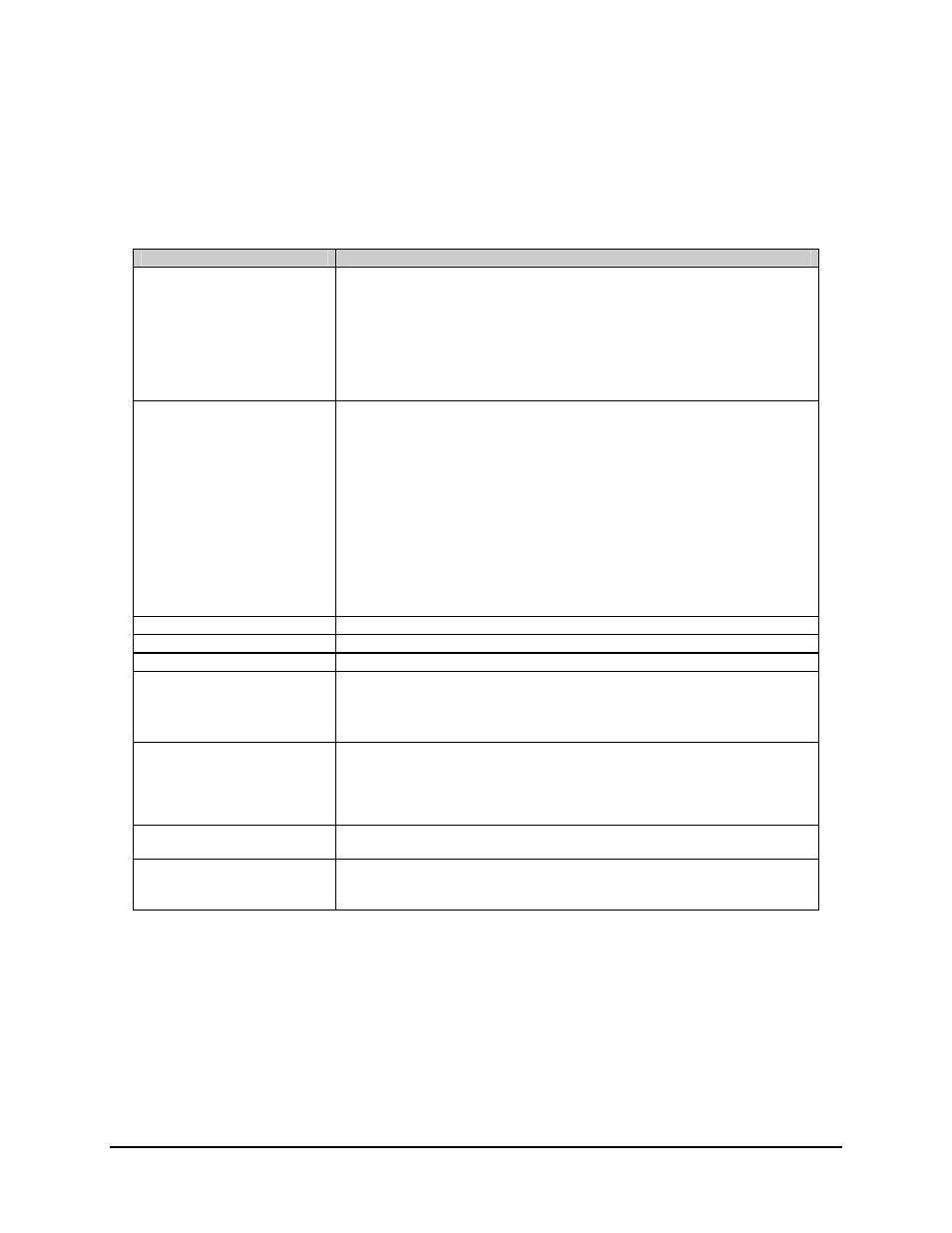

Table 5-4. DEMUX 8-Channel Specification

Parameter

Specification

Aggregate Input:

Type

Data/Clock Interface

Data Rate

Clock

Multiplex Technique

Overhead

Synchronous (clock/data).

TTL (inverted data). Data valid on rising edge of clock.

4001.3 kbit/s maximum, the aggregate data rate is the sum of all tributary data rates

plus the multiplex overhead.

50% duty cycle,

± 10%.

Data interleaved time division.

1.3 kbit/s fixed per frame.

Tributary Outputs:

Number of Channels

Data Rate

Type

Data Interface

Clock

1 to 8

600 bit/s to 4000 kbps, (configurable for each tributary in 100 bit/s increments).

Notes:

1. RS-232 maximum data rate is 64 kbit/s.

2. The sum of all tributary data rates plus overhead cannot exceed the

maximum aggregate data rate of 4001.3 kbit/s.

Synchronous clock and data.

RS-422 or RS-232.

50% duty cycle,

± 10%, phase locked to aggregate clock input, 0.25 dB maximum

jitter gain from aggregate clock input.

Lock Time

1 second maximum after demodulator Carrier Detect.

Operational BER Performance

Will lock and maintain synchronization with BER

≥10

-3

.

Input Power

5 VDC,

± 10%, 900 mA maximum.

Environmental:

Operating Temperature

Storage Temperature

Humidity

-20

° to +60°C (-4° to 140°F)

-55

° to +125°C (-67° to 257°F)

≤ 95% Non-condensing.

Interface Connectors:

JP1

JP2

*JP3

*JP4

+5 VDC power, aggregate data, I

2

C communications to demodulator card.

Output sync and mode signals.

26-pin header, for tributary interfaces 1 through 4.

26-pin header, for tributary interfaces 5 through 8.

Breakout Panel

Optional: 1 RU breakout panel (UB-54) converts interface to eight 15-pin D sub

connector for separate tributary interfaces.

Unit-to-Unit Delay Variation

< 10% of 1/tributary data rate for identically configured demultiplexers.

Note: This is in addition to the delay variation of the base unit.

*Note: JP3 and JP4 headers are connected to the rear panel 25-pin D connectors J5 and J6 respectively

(refer to Section A.3.4).

5-10