Altera Transceiver Signal Integrity Development Kit, Stratix V GX Edition User Manual

Page 19

Chapter 2: Board Components

2–11

MAX II CPLD System Controller

July 2012

Altera Corporation

Transceiver Signal Integrity Development Kit

Stratix V GX Edition Reference Manual

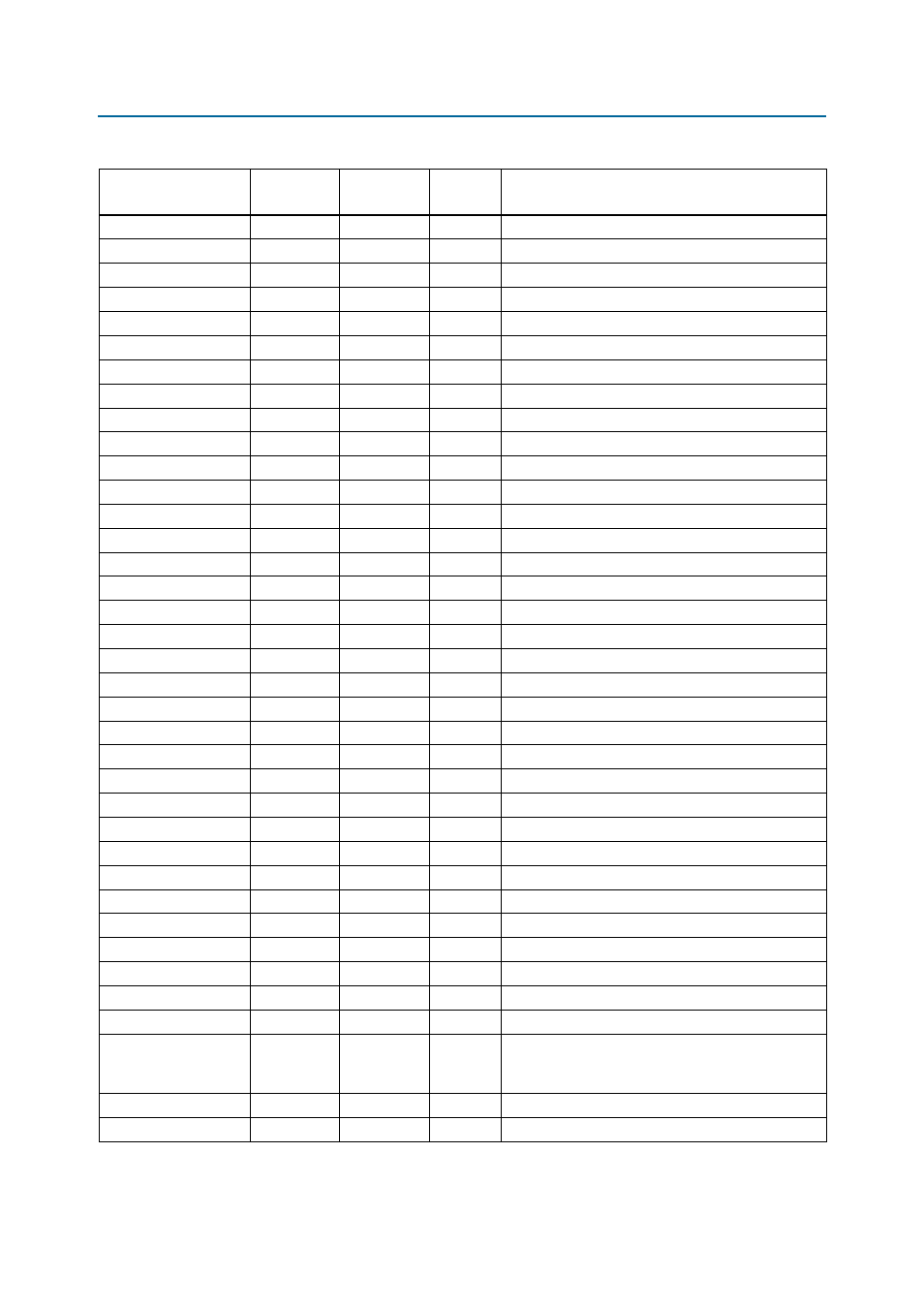

F_AD23

A13

AL12

2.5-V

Flash address bus

F_AD24

B14

AL11

2.5-V

Flash address bus

F_AD25

C13

AM13

2.5-V

Flash address bus

F_AD26

B16

AL13

2.5-V

Flash address bus

F_ADVn

P13

AP7

2.5-V

Flash address valid

F_BSYn

J14

AR7

2.5-V

Flash chip busy

F_CEn

P14

AP9

2.5-V

Flash chip enable

F_CLK

R16

AN6

2.5-V

Flash clock

F_D0

L15

AN11

2.5-V

Flash data bus

F_D1

L16

AM11

2.5-V

Flash data bus

F_D2

K15

AP12

2.5-V

Flash data bus

F_D3

K16

AN12

2.5-V

Flash data bus

F_D4

H16

AN10

2.5-V

Flash data bus

F_D5

H15

AM10

2.5-V

Flash data bus

F_D6

G16

AR11

2.5-V

Flash data bus

F_D7

G15

AR10

2.5-V

Flash data bus

F_D8

M13

AT12

2.5-V

Flash data bus

F_D9

L13

AU13

2.5-V

Flash data bus

F_D10

J13

AU12

2.5-V

Flash data bus

F_D11

H13

AU11

2.5-V

Flash data bus

F_D12

G13

AT11

2.5-V

Flash data bus

F_D13

F13

AW13

2.5-V

Flash data bus

F_D14

F14

AV13

2.5-V

Flash data bus

F_D15

E14

AW11

2.5-V

Flash data bus

F_OEn

P15

AN9

2.5-V

Flash output enable

F_RSTn

H14

AL8

2.5-V

Flash reset

F_WEn

G14

AM8

2.5-V

Flash write enable

F_WPn

T12

AP6

2.5-V

Flash write protect

FACTORY_IMAGE

R8

—

2.5-V

Factory image for configuration

FAN_CTRL

E3

D6

2.5-V

Fan control

FAN_LED

C3

C6

2.5-V

Fan LED

INIT_DONE

R13

AN33

2.5-V

FPGA initialization done.

JTAG_TCK

P3

AV34

2.5-V

JTAG chain clock

JTAG_TMS

N4

AU34

2.5-V

JTAG chain mode

MAX_2_MAX_INITDONE

H2

—

2.5-V

Control signal between the MAX II System Controller

and the MAX II embedded USB-Blaster to indicate that

initialization is done.

MAX_FPP_TDI

L6

—

2.5-V

Fast Passive Parallel (FPP) programming data in

MAX_FPP_TDO

M5

—

2.5-V

FPP programming data out

Table 2–5. MAX II CPLD System Controller Device Pin-Out (Part 3 of 5)

Schematic Signal

Name

MAX II CPLD

Pin Number

Stratix V GX

Pin Number

i/O

Standard

Description