Altera Stratix IV GX FPGA Development Board User Manual

Page 52

2–44

Chapter 2: Board Components

Components and Interfaces

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

November 2010

Altera Corporation

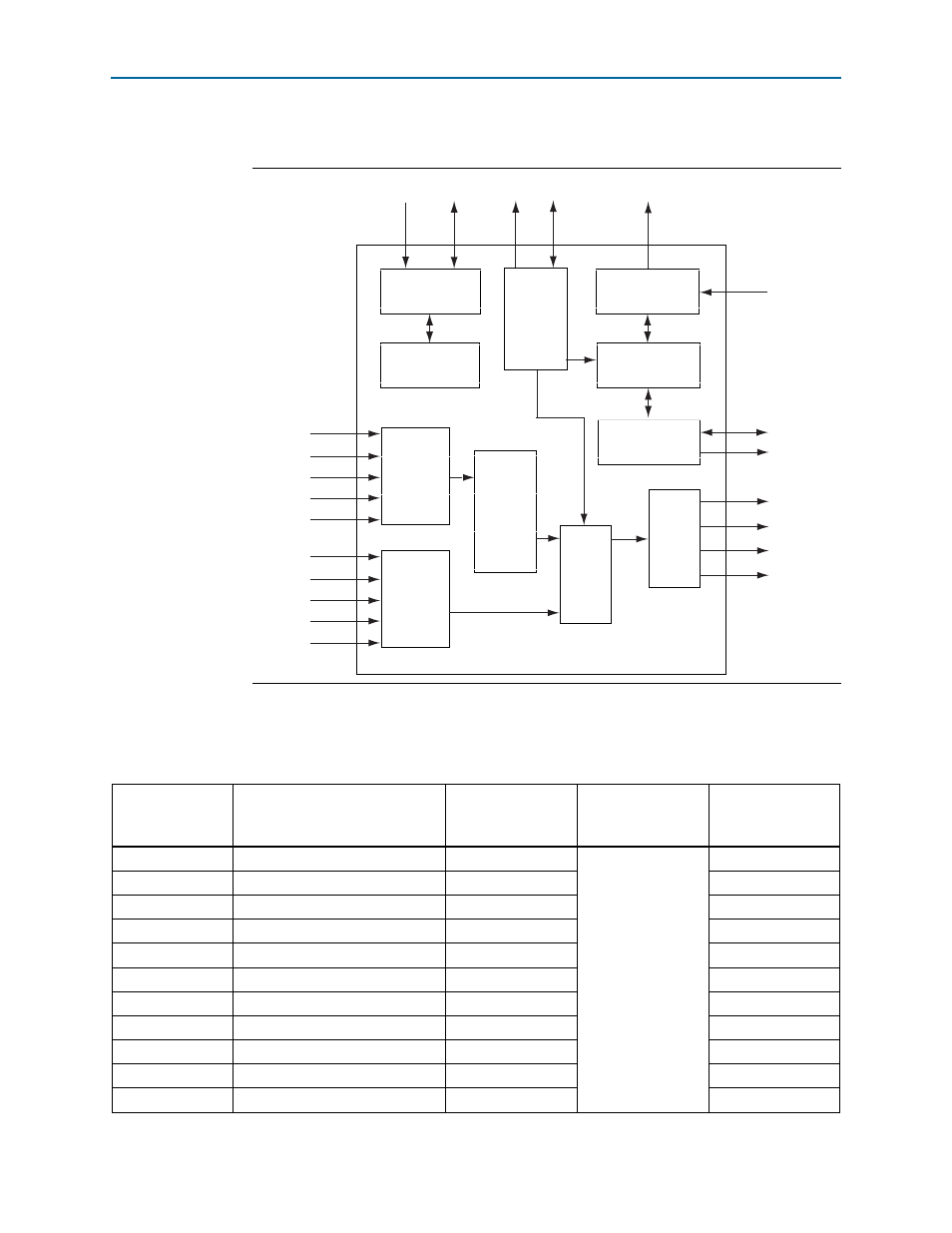

shows a block diagram of the AD9889B HDMI transmitter device.

summarizes the HDMI video output interface pin assignments, signal

names, and functions.

Figure 2–12. AD9889B HDMI Transmitter Device Block Diagram

Video

Data

Capture

Audio

Data

Capture

Color

Space

Conversion

4:2:2 to 4:4:4

Conversion

XOR

Mask

HDMI

Tx

Core

HDCP

Core

I

2

C Slave

Register Configuration

Logic

I

2

C Master

HDCP-EDID

Microcontroller

Interrupt

Handler

AD9889B

SCL

SDA

MCL

MDA

INT

HPD

DDCSDA

DDCSCL

Tx0– /Tx0+

Tx1– / Tx1+

Tx2– / Tx2+

TxC– / TxC+

SCLK

LRCLK

MCLK

S/PDIF

D [23:0]

DE

HSYNC

VSYNC

CLK

I

2

S [3:0]

Table 2–40. HDMI Video Output Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 2)

Board Reference

Description

Schematic Signal

Name

I/O Standard

Stratix IV GX

Device

Pin Number

U25.B1

Video data bus

HDMI_D0

1.8-V

AW34

U25.A1

Video data bus

HDMI_D1

AL25

U25.B2

Video data bus

HDMI_D2

AK25

U25.A2

Video data bus

HDMI_D3

AP26

U25.B3

Video data bus

HDMI_D4

AH26

U25.A3

Video data bus

HDMI_D5

AM26

U25.B4

Video data bus

HDMI_D6

AK26

U25.A4

Video data bus

HDMI_D7

AN26

U25.B5

Video data bus

HDMI_D8

AP27

U25.A5

Video data bus

HDMI_D9

AN27

U25.B6

Video data bus

HDMI_D10

AV28