10/100/1000 ethernet, 10/100/1000 ethernet –33 – Altera Stratix IV GX FPGA Development Board User Manual

Page 41

Chapter 2: Board Components

2–33

Components and Interfaces

November 2010

Altera Corporation

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

10/100/1000 Ethernet

A Marvell 88E1111 PHY device is used for 10/100/1000 BASE-T Ethernet connection.

The device is an auto-negotiating Ethernet PHY with an SGMII interface to the FPGA.

The Stratix IV GX device can communicate with the LVDS interfaces at up to 1.6 Gbps,

which is faster than 1.25 Gbps for SGMII. The MAC function must be provided in the

FPGA for typical networking applications. The Marvell 88E1111 PHY uses 2.5-V and

1.1-V power rails and requires a 25-MHz reference clock driven from a dedicated

oscillator. It interfaces to an RJ-45 with internal magnetics that can be used for driving

copper lines with Ethernet traffic.

J17.B38

Add-in card receive bus

PCIE_RX_N5

1.4-V PCML

AC39

J17.B33

Add-in card receive bus

PCIE_RX_P4

AE38

J17.B34

Add-in card receive bus

PCIE_RX_N4

AE39

J17.B27

Add-in card receive bus

PCIE_RX_P3

AG38

J17.B28

Add-in card receive bus

PCIE_RX_N3

AG39

J17.B23

Add-in card receive bus

PCIE_RX_P2

AJ38

J17.B24

Add-in card receive bus

PCIE_RX_N2

AJ39

J17.B19

Add-in card receive bus

PCIE_RX_P1

AR38

J17.B20

Add-in card receive bus

PCIE_RX_N1

AR39

J17.B14

Add-in card receive bus

PCIE_RX_P0

AU38

J17.B15

Add-in card receive bus

PCIE_RX_N0

AU39

J17.A13

Motherboard reference clock

PCIE_REFCLK_P

HCSL

AN38

J17.A14

Motherboard reference clock

PCIE_REFCLK_N

AN39

J17.A11

Reset

PCIE_PERSTn

LVTTL

R32

J17.B11

Wake signal

PCIE_WAKEn

P31

J17.B5

SMB clock

PCIE_SMBCLK

AE31

J17.B6

SMB data

PCIE_SMBDAT

P32

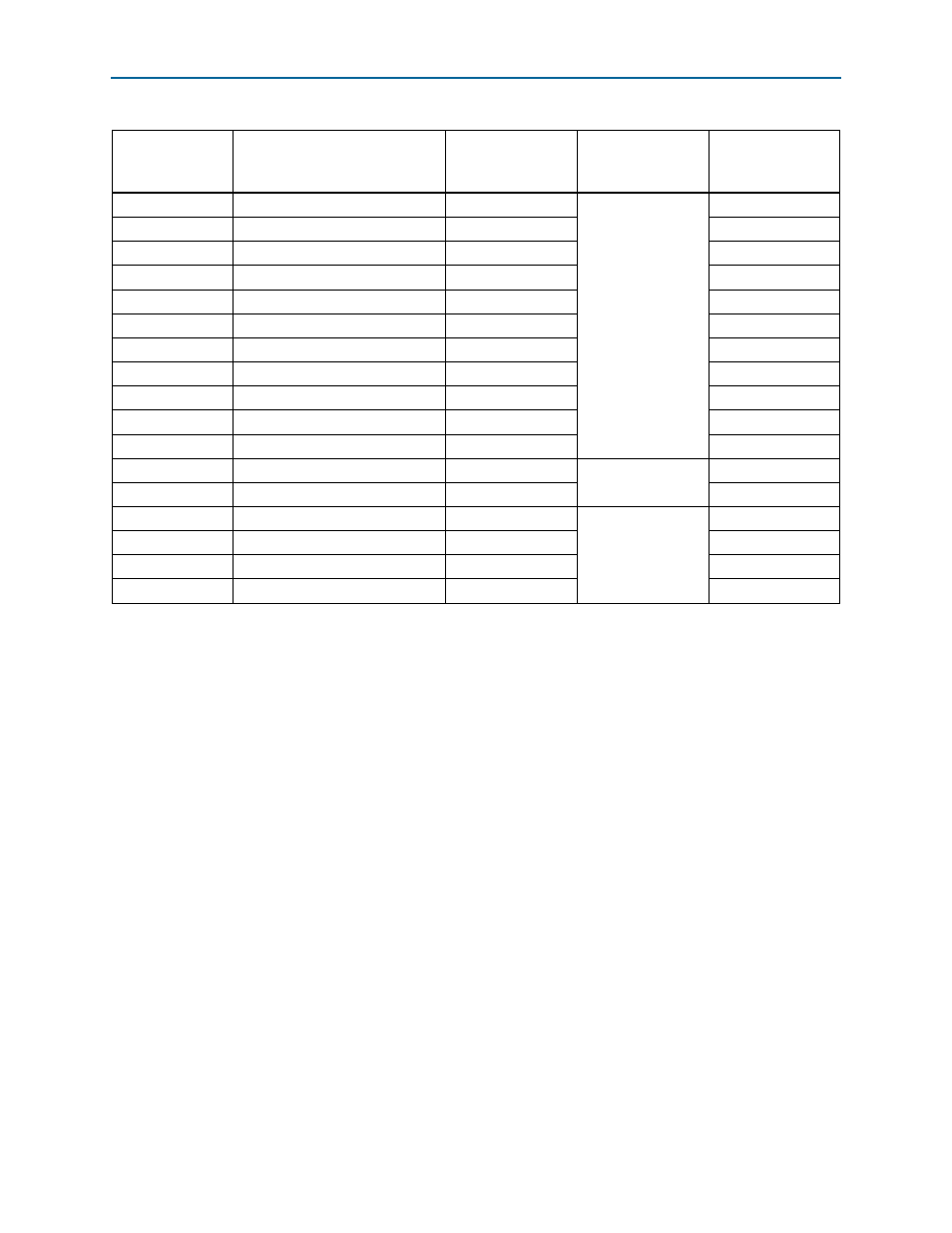

Table 2–34. PCI Express Pin Assignments, Schematic Signal Names, and Functions (Part 2 of 2)

Board Reference

Description

Schematic Signal

Name

I/O Standard

Stratix IV GX

Device

Pin Number