Altera Stratix IV E FPGA User Manual

Page 23

Chapter 4: Development Board Setup

4–7

Factory Default Switch Settings

June 2011

Altera Corporation

Stratix IV E FPGA Development Kit User Guide

f

For more information about the FPGA board settings, refer to the

.

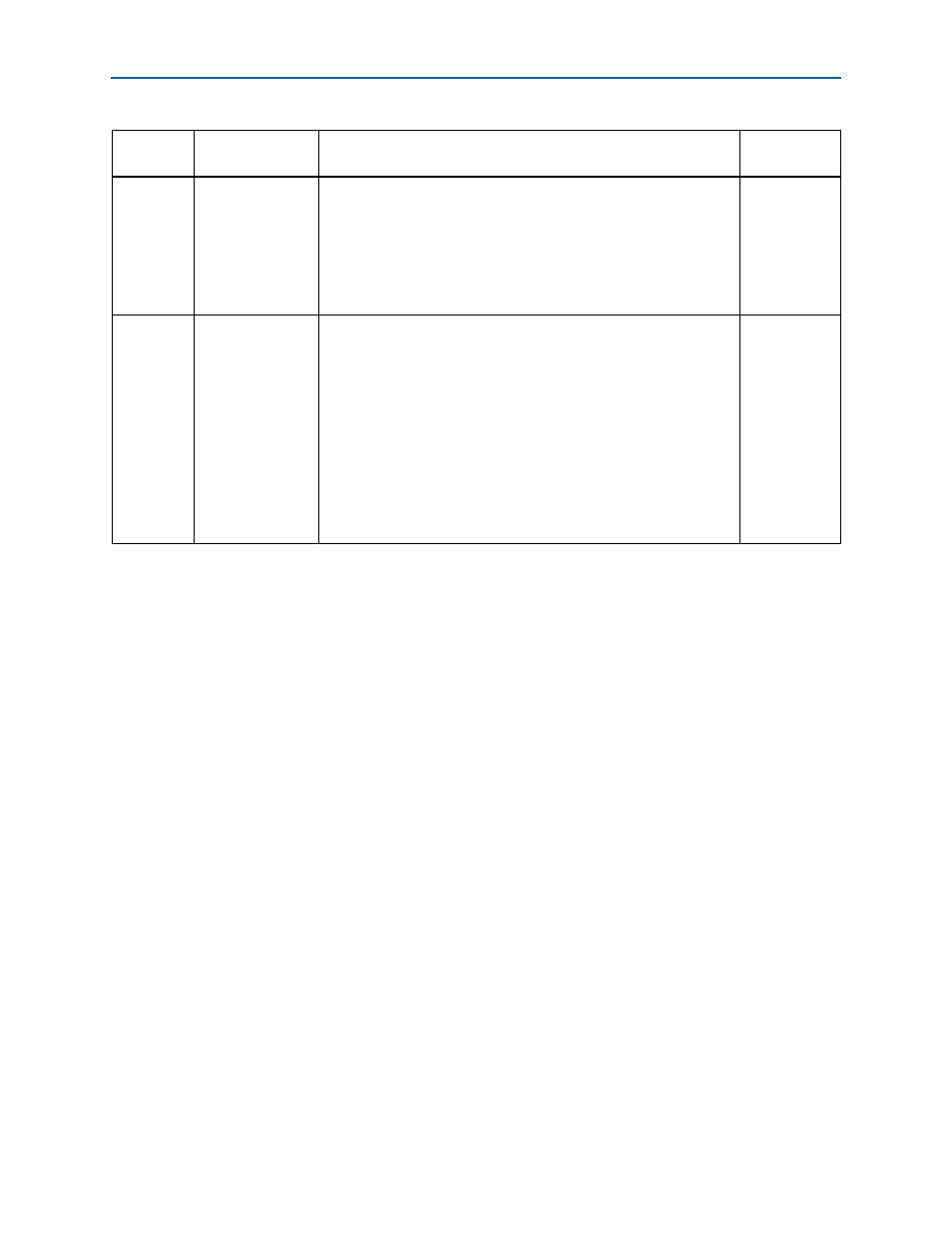

J21

VCC_VCCL_SEL

This jumper has the following options:

■

Installing the shunt on pins 1 and 2 sets VCC and VCCL to 0.9 V.

■

Installing the shunt on pins 2 and 3 sets VCC and VCCL to 1.1 V.

■

Removing the shunt sets VCC and VCCL to 0.6 V.

Always keep a shunt installed on pins 1 and 2 only. The current version

of the Stratix IV E device requires 0.9 V.

Installed on

pins 1 and 2

J28

RLD_ZQ_IMPED

To use the RLDRAM II impedance drive jumpers, set the mode

register. When the mode register is not set, the RLDRAM II output

impedance is 50

Ω. The RLDRAM II impedance drive jumpers have the

following options:

■

Installing the shunt on pins 1 and 2 sets the RLDRAM II output

impedance to the maximum value possible.

■

Installing the shunt on pins 3 and 4 sets the RLDRAM II output

impedance to 50

Ω.

■

Installing the shunt on pins 5 and 6 sets the RLDRAM II output

impedance to 60

Ω.

Installing more than one shunt might cause damage to the device.

Not installed

Table 4–4. Jumper Settings (Part 2 of 2)

Board

Reference

Board

Label

Function

Default

Shunt Position