Alt_bidir_diff, Example 2–14 – Altera Designing With Low-Level Primitives User Manual

Page 44

2–22

Altera Corporation

Designing with Low-Level Primitives User Guide

April 2007

Primitives

Example 2–14. ALT_IOBUF_DIFF Primitive Instantiation, Verilog HDL

module test(in1,in2,oe,out,bidir,bidir_n);

input in1;

input in2;

input oe;

inout bidir;

inout bidir_n;

output out;

wire tmp1;

and(tmp1,in1,in2);

ALT_IOBUF_DIFF inst(.i(tmp1), .oe(oe), .o(out), .io(bidir),

.iobar(bidir_n));

defparam inst.io_standard = "LVDS";

defparam inst.current_strength = "12mA";

endmodule

ALT_BIDIR_DIFF

This primitive allows you to name and connect positive and negative pins

when the altddio_bidir megafunction is used your design. You can assign

I/O standard, location, drive strength (current strength), slew rate, and

termination assignments, control bus hold circuitry, and enable weak

pull-up resistor on the

bidir pins. An attempt to set any other parameter

will result in an error.

lists the ports and parameters of the

ALT_BIDIR_DIFF

primitive, and their respective description and possible values.

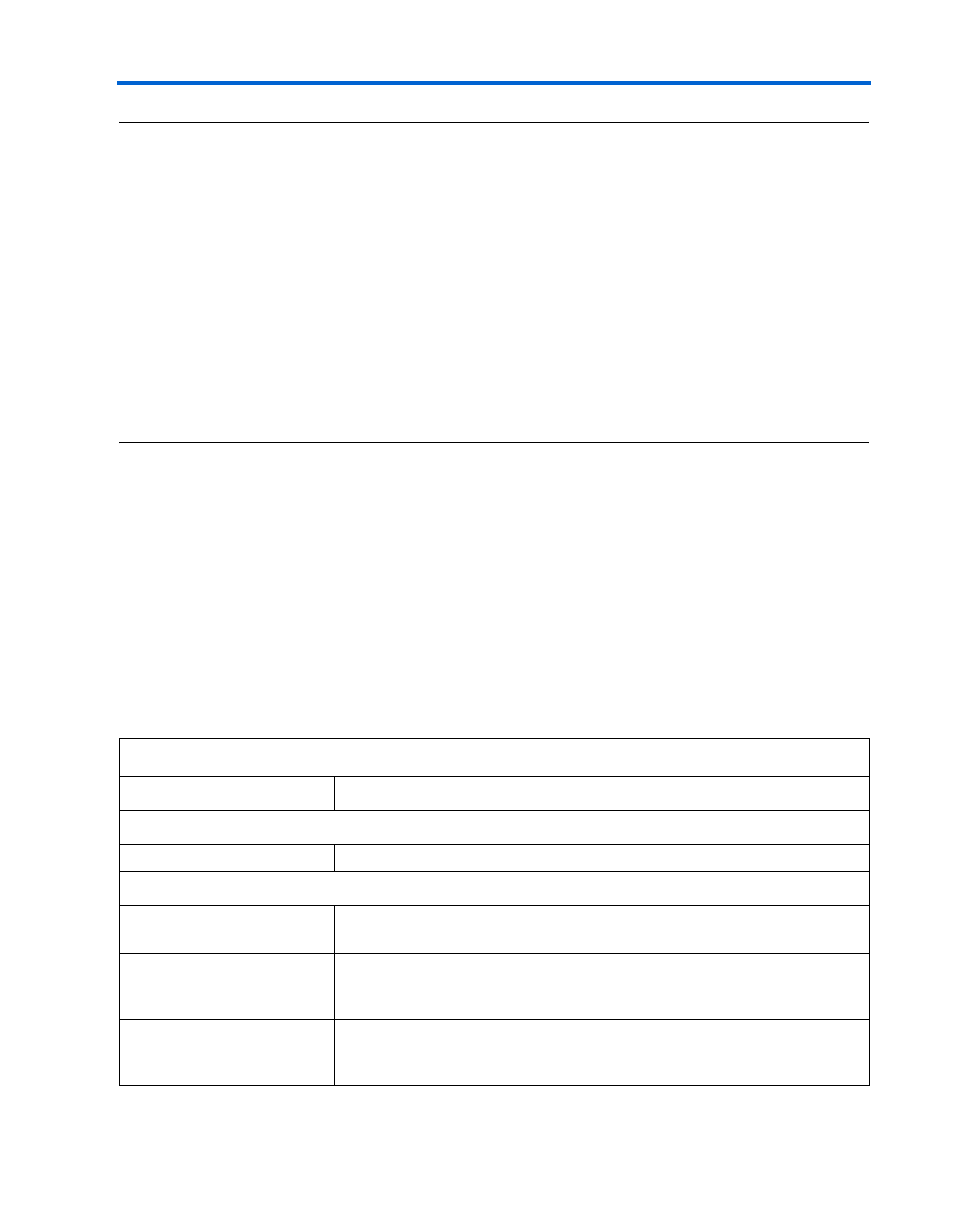

Table 2–9. ALT_BIDIR_DIFF Ports and Parameters (Part 1 of 2)

Port/Parameter

Description/Value

Input Ports

oe

Connect this port to the

oe_out

port of the altddio_bidir megafunction.

Bidirectional Port

bidirin

Connect this port to the

padio

port of the altddio_bidir megafunction. The

padio

port should not have any other fan-outs.

io

This port represents the positive pin of a differential I/O standard.

Connect this port to the device’s

bidir

pin or an entity

bidir

port. There

must be no logic between the

io

port and the chip

bidir

port.

iobar

This port represents the negative pin of a differential I/O standard.

Connect this port to the device's

bidir

pin or an entity

bidir

port. There

must be no logic between the

iobar

port and the chip

bidir

port.