Table 2–1 – Altera Designing With Low-Level Primitives User Manual

Page 24

2–2

Altera Corporation

Designing with Low-Level Primitives User Guide

April 2007

Primitives

the input and output ports and the parameters associated with

ALT_INBUF. If any other parameter is specified (for example,

current_strength) an error will result.

shows a Verilog HDL example of an

ALT_INBUF primitive

instantiation.

Example 2–1. ALT_INBUF Primitive Instantiation, Verilog HDL

alt_inbuf my_inbuf (.i(in), .o(internal_sig));

//in must be declared as an input pin

defparam my_inbuf.io_standard = "2.5 V";

defparam my_inbuf.location = "IOBANK_2";

defparam my_inbuf.enable_bus_hold = "on";

defparam my_inbuf.weak_pull_up_resistor = "off";

defparam my_inbuf.termination = "parallel 50 ohms";

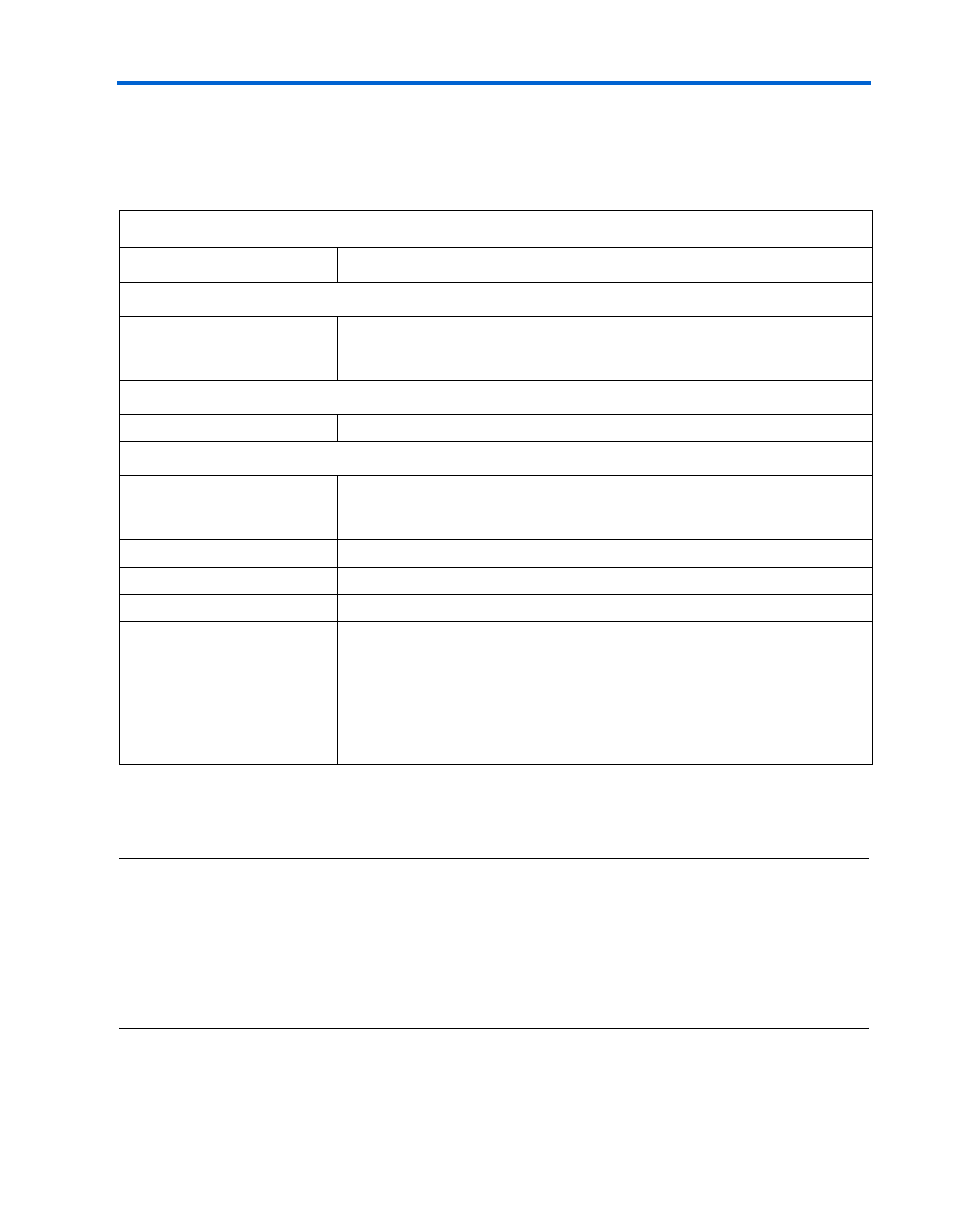

Table 2–1. ALT_INBUF Ports and Parameters

Port/Parameter

Description/Value

Input Ports

i

Connect this port to a chip input pin or to a wire to be connected to an input pin.

There must be no logic between the i port and the chip input pin. If there is, an

error results.

Output Ports

o

Connect this port to the logic in the design to receive the input signal.

Parameter

io_standard

A logic option that specifies the I/O standard of a pin. Different device families

support different I/O standards, and restrictions apply to placing pins with

different I/O standards together.

location

Any legal pin location for the current device.

enable_bus_hold

An option to enable bus-hold circuitry. Legal values are “

on

” and “

off

.”

weak_pull_up_resistor

An option to enable the weak pull-up resistor. Legal values are “

on

” and “

off

.”

termination

Any legal on-chip-termination value for the current device. For GX families, this

parameter supports only regular termination, and not GXB termination. For GX

families, you must use Assignment Editor in the Quartus II software to set the

type of termination on high-speed transceivers.

This parameter is supported for Stratix III, Stratix II, Stratix II GX, HardCopy

®

II

and Cyclone II.