Altera Designing With Low-Level Primitives User Manual

Page 32

2–10

Altera Corporation

Designing with Low-Level Primitives User Guide

April 2007

Primitives

Example 2–8. ALT_IOBUF Primitive Component Declaration, VHDL

COMPONENT alt_iobuf

GENERIC (

IO_STANDARD : STRING :="NONE";

CURRENT_STRENGTH : STRING :="NONE";

SLOW_SLEW_RATE : STRING :="NONE";

LOCATION : STRING :="NONE";

ENABLE_BUS_HOLD : STRING :="NONE";

WEAK_PULL_UP_RESISTOR : STRING :="NONE";

TERMINATION : STRING :="NONE";

INPUT_TERMINATION : STRING := "NONE" ;

OUTPUT_TERMINATION : STRING := "NONE";

SLEW_RATE:INTEGER := -1

);

PORT (

i : IN STD_LOGIC;

oe: IN STD_LOGIC;

io : INOUT STD_LOGIC;

o : OUT STD_LOGIC );

END COMPONENT;

output_termination

Any legal output on-chip termination value for the current device. This

parameter cannot be used with the termination parameter. this parameter is

supported in Stratix III and Cyclone III devices.

slow_slew_rate

A logic option that implements slow low-to-high or high-to-low transitions on

output pins to help reduce switching noise. Current legal values are “

on

” and

“

off

.”

This assignment is ignored by the Fitter for Stratix II and Cyclone II devices.

This parameter is not supported for Stratix II GX or HardCopy II devices.

slew_rate

The

slow_slew_rate

parameter is not available for Stratix III and

Cyclone III. These two families support the

slew_rate

parameter instead.

Accepts any positive integer value including 0. Default value is –1, which is

equivalent to not using this parameter. Available only for Stratix III and

Cyclone III.

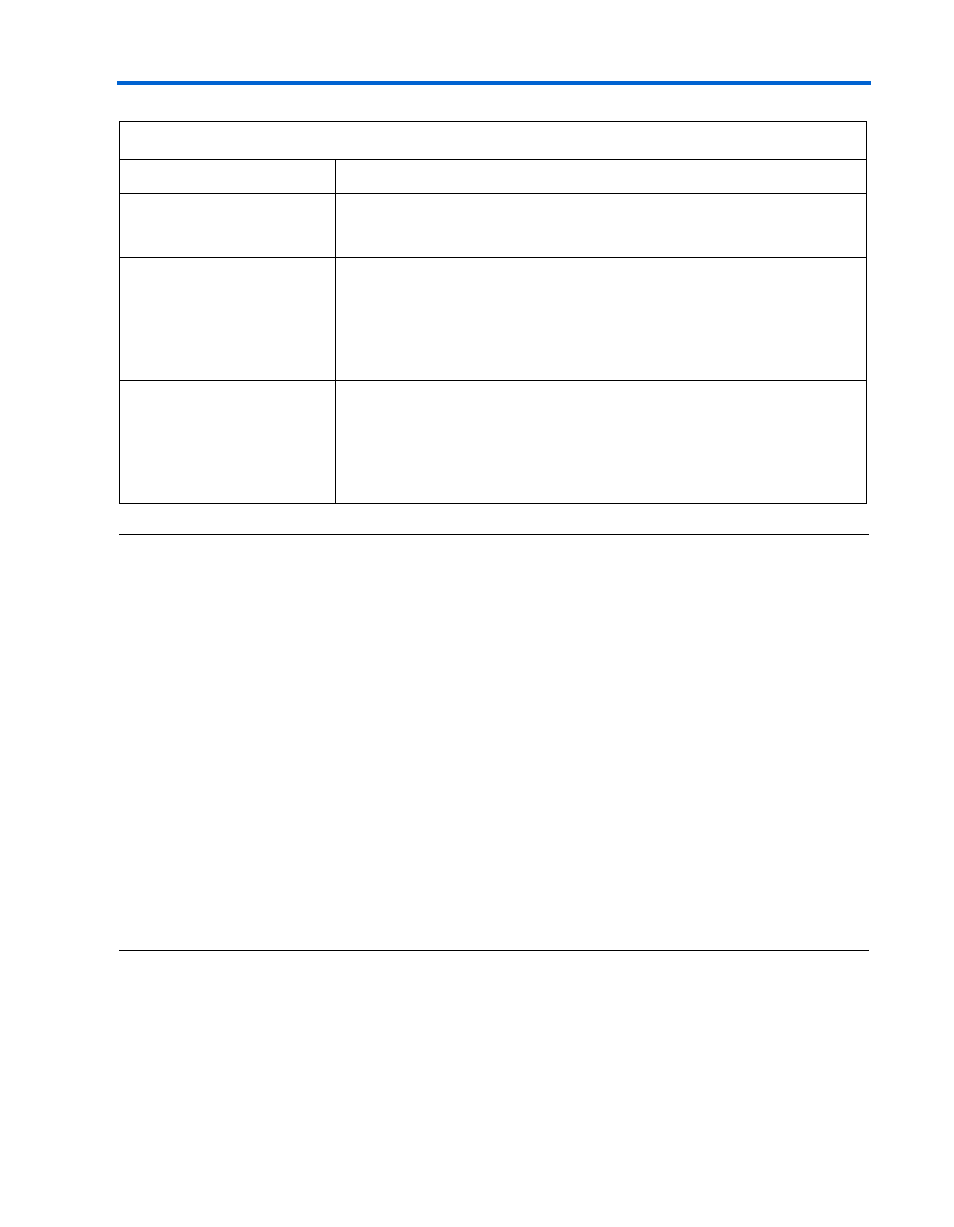

Table 2–4. ALT_IOBUF Ports and Parameters

Port/Parameter

Description/Value