Altera Designing With Low-Level Primitives User Manual

Page 42

2–20

Altera Corporation

Designing with Low-Level Primitives User Guide

April 2007

Primitives

Each parameter except

slew_rate also accepts the value “none”.

Assigning the value “none” to any such parameter is equivalent to not

setting the parameter. The parameter

slew_rate accepts the value –1 as

the default. Assigning –1 to

slew_rate is equivalent to not setting the

parameter. Note that the primitive requires that all five ports (

i, oe, o, io,

and

iobar) are connected. Also note that all parameters are optional.

shows an example of a VHDL component instantiation,

and

shows a Verilog HDL example of an

ALT_IOBUF_DIFF primitive instantiation.

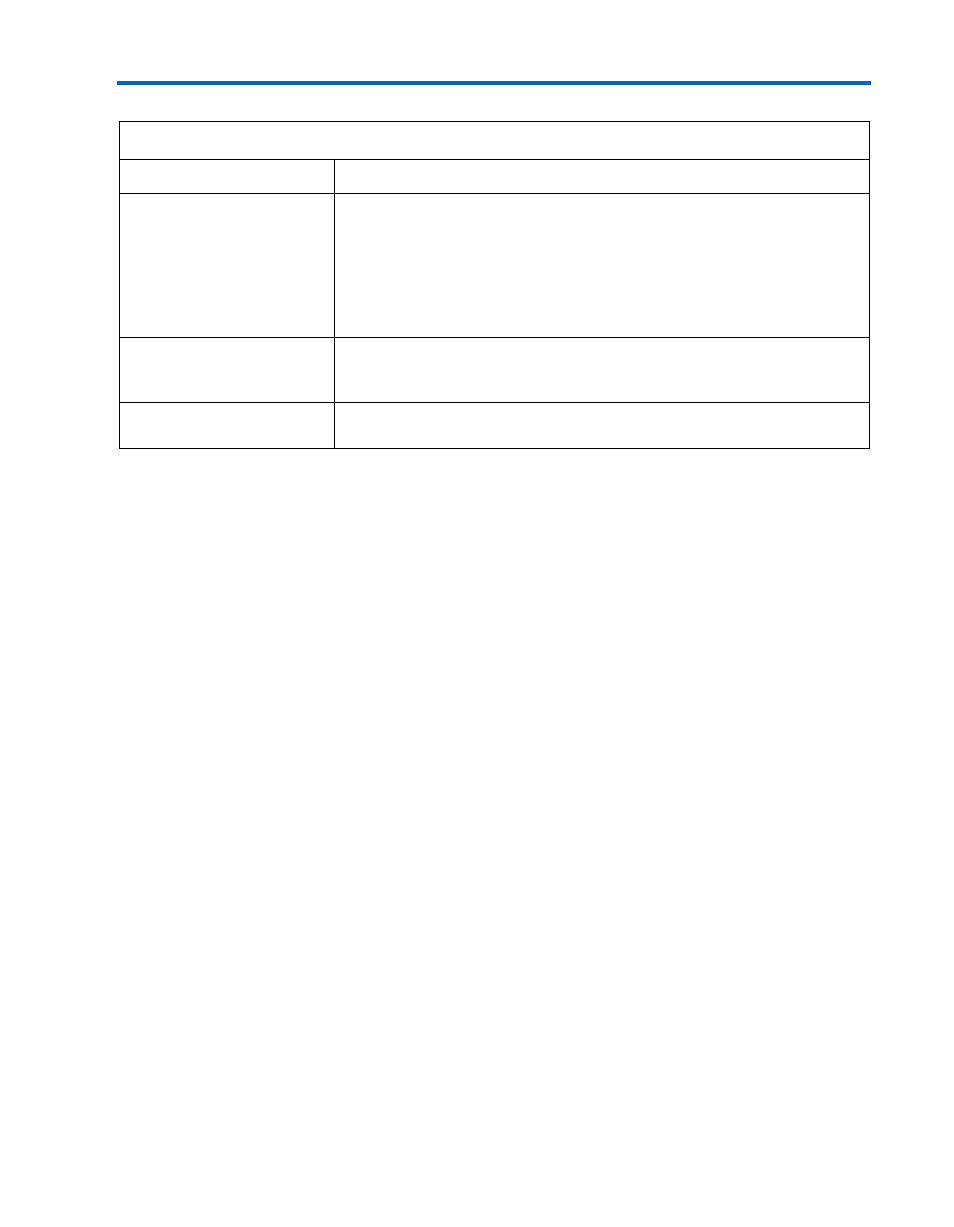

termination

Any legal on-chip-termination value for the current device. This value is set as

the input as well as the output termination value for the current device. To set

separate input and output values, use

input_termination

and

output_termination

parameters instead.

This parameter cannot be used with

input_termination

or

output_termination

.

input_termination

Any legal input on-chip-termination value for the current device. This parameter

cannot be used with the

termination

parameter.

Note: The Fitter ignores this parameter for Cyclone III devices.

output_termination

Any legal output on-chip-termination value for the current device. This

parameter cannot be used with the

termination

parameter.

Table 2–8. ALT_IOBUF_DIFF Ports and Parameters (Part 2 of 2)

Port/Parameter

Description/Value