Altera ASI MegaCore Function User Manual

Page 21

4–6

Chapter 4: Functional Description

Signals

Asynchronous Serial Interface (ASI) MegaCore Function User Guide

January 2014

Altera Corporation

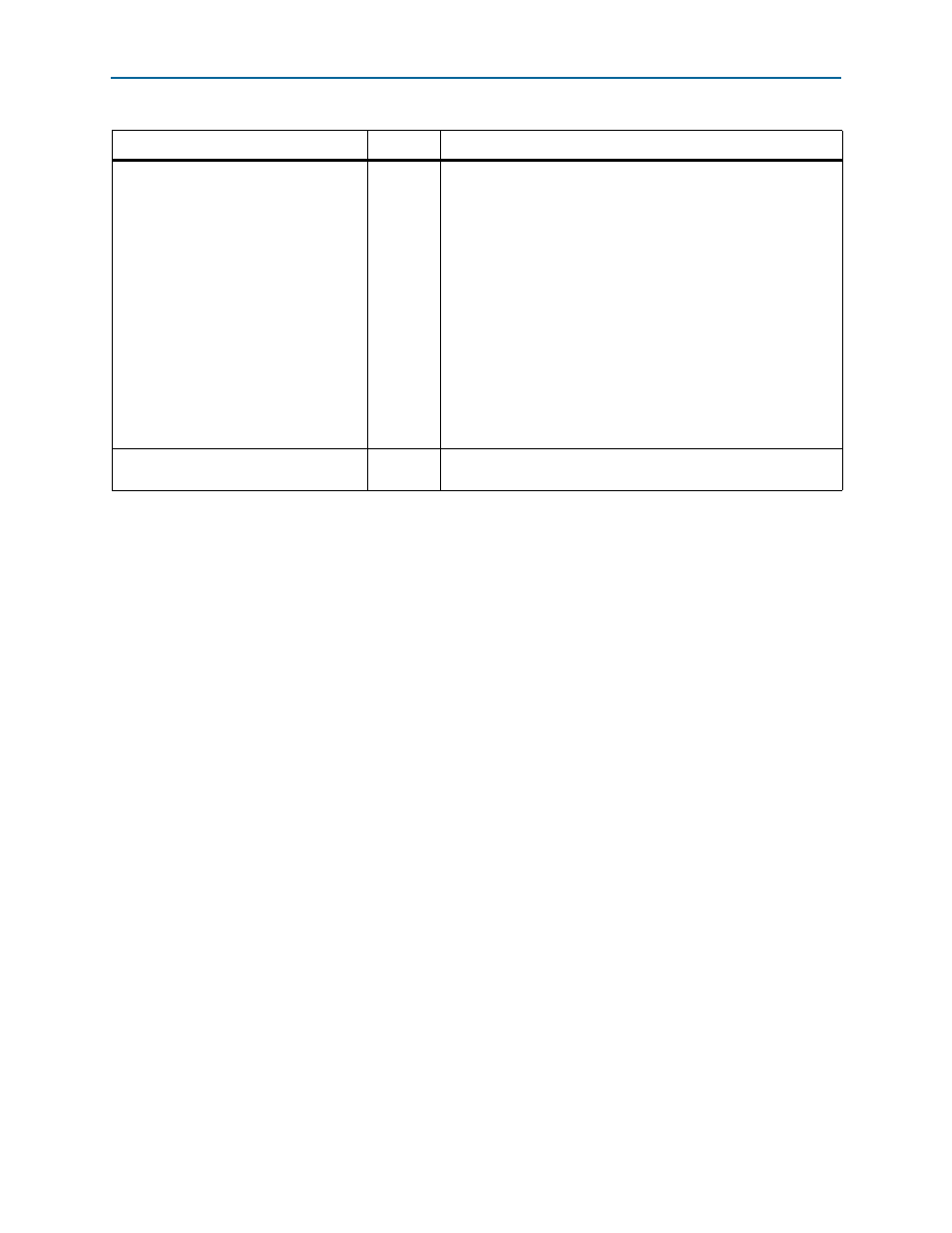

rx_ts_status[7:0]

Output

TS status bits.

0 indicates receiver data valid

1 indicates start of packet

2 indicates end of packet

3 indicates receiver error

5:4 indicates 00 is unlocked; 01 is 204 byte packet lock, 11 is 188

byte packet lock

6 indicates TS serial polarity

7 indicates that the data on rx_data[7:0] is a valid word from the

8B10B decoder. Unlike rx_ts_status[0], this signal is not

dependent on the correct packet or synchronization structure of the

stream.

tx_protocol_out[9:0]

Output

Output from transmitter protocol block for split

protocol/transceiver mode.

Notes for

Table 4–1

:

(1) This signal is available for Stratix IV transceivers only.

(2) In Quartus II version 8.1 and later, the Stratix IV transceivers need RX buffer calibration through an altgx_reconfig (DPRIO) controller. You

must connect the ports to the altgx_reconfig controller externally. For further information on the RX buffer calibration, refer to Stratix IV

DPRIO documentation. If you are using Quartus II software version 13.1, upgrade the ASI MegaCore function to version 13.1 as well.

Table 4–1. Signals (Part 2 of 2)

Signal

Direction

Description