Testbench, Signals, Testbench –5 signals –5 – Altera ASI MegaCore Function User Manual

Page 20

Chapter 4: Functional Description

4–5

Testbench

January 2014

Altera Corporation

Asynchronous Serial Interface (ASI) MegaCore Function User Guide

Testbench

The testbench instantiates two ASI MegaCore functions—one ASI transmitter, one

ASI receiver.

To test a realistic ASI link, an ASI packet generator creates packets that are sent from

the instantiation of the ASI transmitter to the instantiation of the ASI receiver. A

random serial data delay generator is inserted on the way to mimic random jitter on

the link. The transmitter and receiver are clocked with asynchronous clock sources—

the frequencies differ by 200 ppm, which maximizes the stress that the ASI receiver

sees and is similar to a real link.

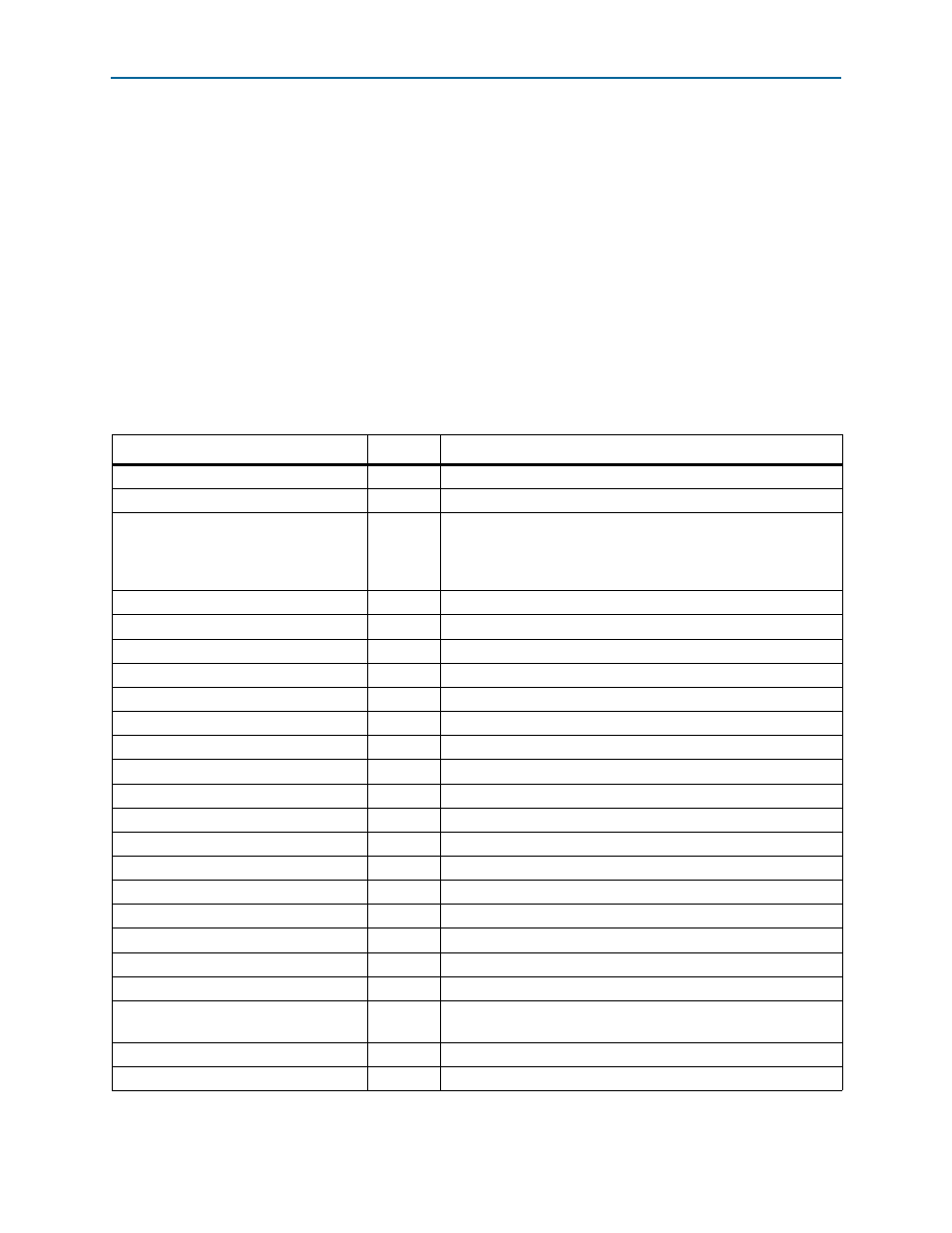

Signals

Table 4–1

shows the signals.

Table 4–1. Signals (Part 1 of 2)

Signal

Direction

Description

asi_rx

Input

ASI input.

cal_blk_clk

Input

Calibration clock for hard transceiver.

gxb_powerdown

Input

Transceiver block reset and power down. This signal of all the

instances that are to be combined into a single transceiver block

must be connected to a single point; for example, the same input

pin or same logic.

reconfig_clk

Input

Clock input for the embedded transceiver instance.

reconfig_togxb[3:0]

Input

Data input for the embedded transceiver instance.

rst

Input

Reset.

rx_clk135

Input

135-MHz clock from external PLL.

rx_protocol_in[9:0]

Input

Protocol input (for split SERDES/protocol).

rx_protocol_in_valid

Input

Valid signal for rx_protocol_in.

rx_serial_clk

Input

337.5-MHz clock from external PLL.

rx_serial_clk90

Input

337.5-MHz clock from external PLL with + 90

phase shift.

tx_clk270

Input

270-MHz clock from external PLL.

tx_clk135

Input

135-MHz clock from external PLL (only for hard SERDES).

tx_data[7:0]

Input

TS parallel data input into encoder.

tx_en

Input

Transmit enable. Assert to indicate valid data on tx_data.

tx_refclk

Input

27-MHz reference clock for transmitter.

tx_serdes_in[9:0]

Input

Direct input to transceiver block for split protocol/tranceiver mode.

asi_tx

Output

ASI output.

reconfig_fromgxb[16:0]

Output

Data output from the embedded transceiver instance.

rx_data[7:0]

Output

Decoded parallel TS data out of receiver.

rx_data_clk

Output

135-MHz parallel clock, which you can use to clock

rx_data[7:0]

.

rx_serdes_out[9:0]

Output

Raw data from transceiver block before decoding.

rx_serdes_out_valid

Output

Valid signal out of the transceiver.