3 addresses in the process image, Addresses in the process image – Pilz PSSu E F DI OZ 2 User Manual

Page 16

Function description

Operating Manual PSSu E F DI OZ 2(T)(R)

21328EN05

16

}

Optimisation of ST process image by combining adjacent bits of the same type.

Configuration „*“

INFORMATION

The PSSuniversal Configurator on the PSS WINPRO system software

must be used to define the I/OGroups to which FS inputs and outputs be

long (SafetyBUS p). The PSSu can be divided into sections A and B for this

purpose.

All the FS outputs on a PSSu always belong to section A.

All the FS inputs on a PSSu always belong to section B.

Section A and section B on a PSSu may belong to different I/OGroups.

Further information on configuration is available in the PSSuniversal Configurator's online

help.

4.2.1.3

Addresses in the process image

The module occupies two consecutive bit addresses for the input in the FSPII:

}

Bit address 1: Input I0 for connecting the feedback loop (connection terminal).

}

Bit address 2: Internal FS input I1 for transmitting open circuit detection (no connection

terminal!).

The module occupies one bit address for the output in the FSPIO.

The display in the ST process image depends on the configuration. With read access ("R"),

the sequence in the STPII is:

}

Bit address 1: FS output O0+

}

Bit address 2: Input I0 for connecting the feedback loop

}

Bit address 3: Internal FS input I1 for transmitting open circuit detection

With write access ("&"), the Bit in the STPIO is used to switch the FS output with the local

enable principle.

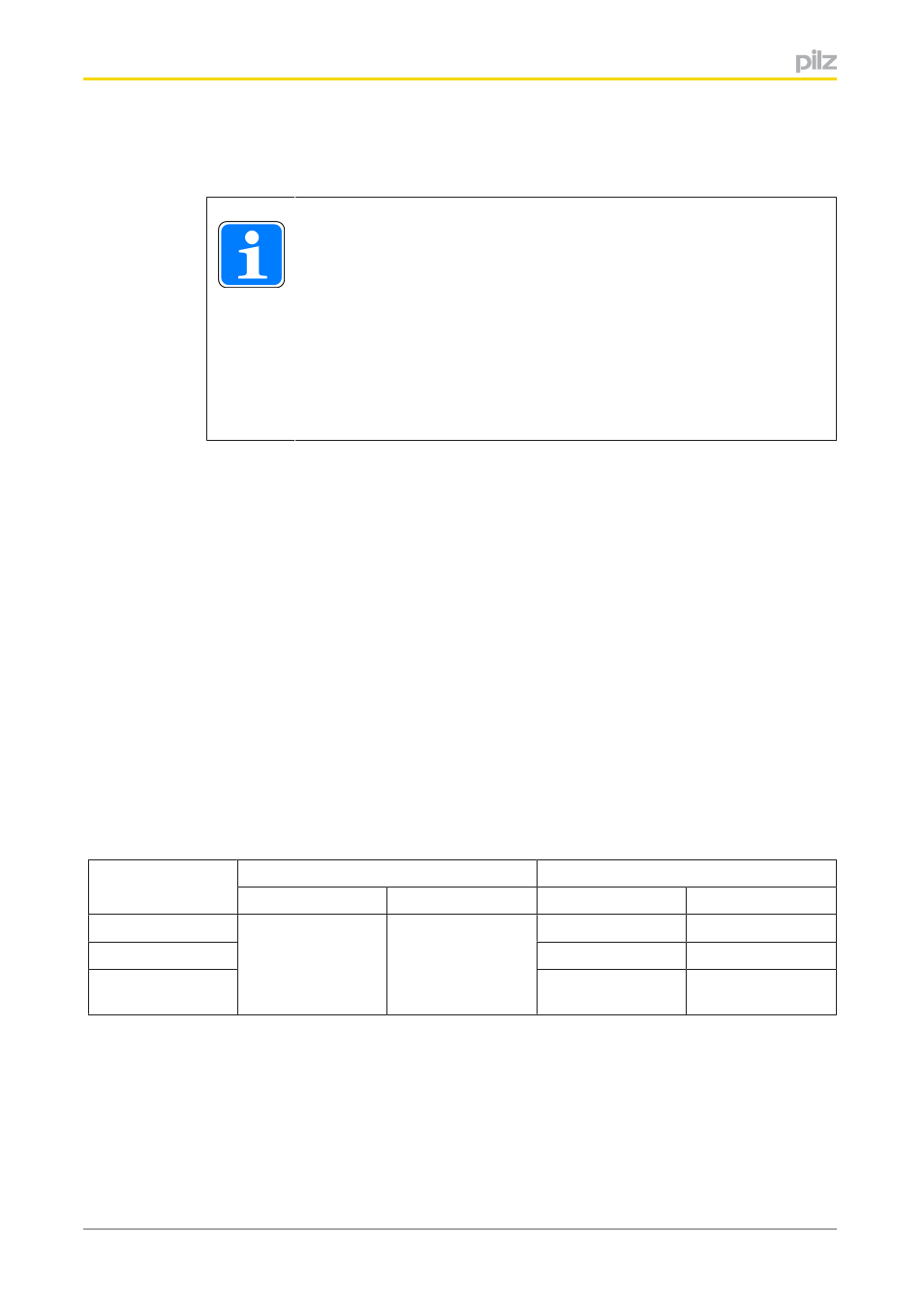

Configuration

SafetyBUS p

Standard bus system

FSPII

FSPIO

STPII

STPIO

None

2 Bit

(e.g.: 32.00 …

32.01)

(e.g.: 32.00)

1 Bit

(e.g.: 32.00)

Read ST (“R”)

3 Bit

ST read and write

(“&”)

3 Bit

1 Bit