Figure 3-11: di timing diagram – ADLINK PCIe-7350 User Manual

Page 47

Function Block and Operation Theory

37

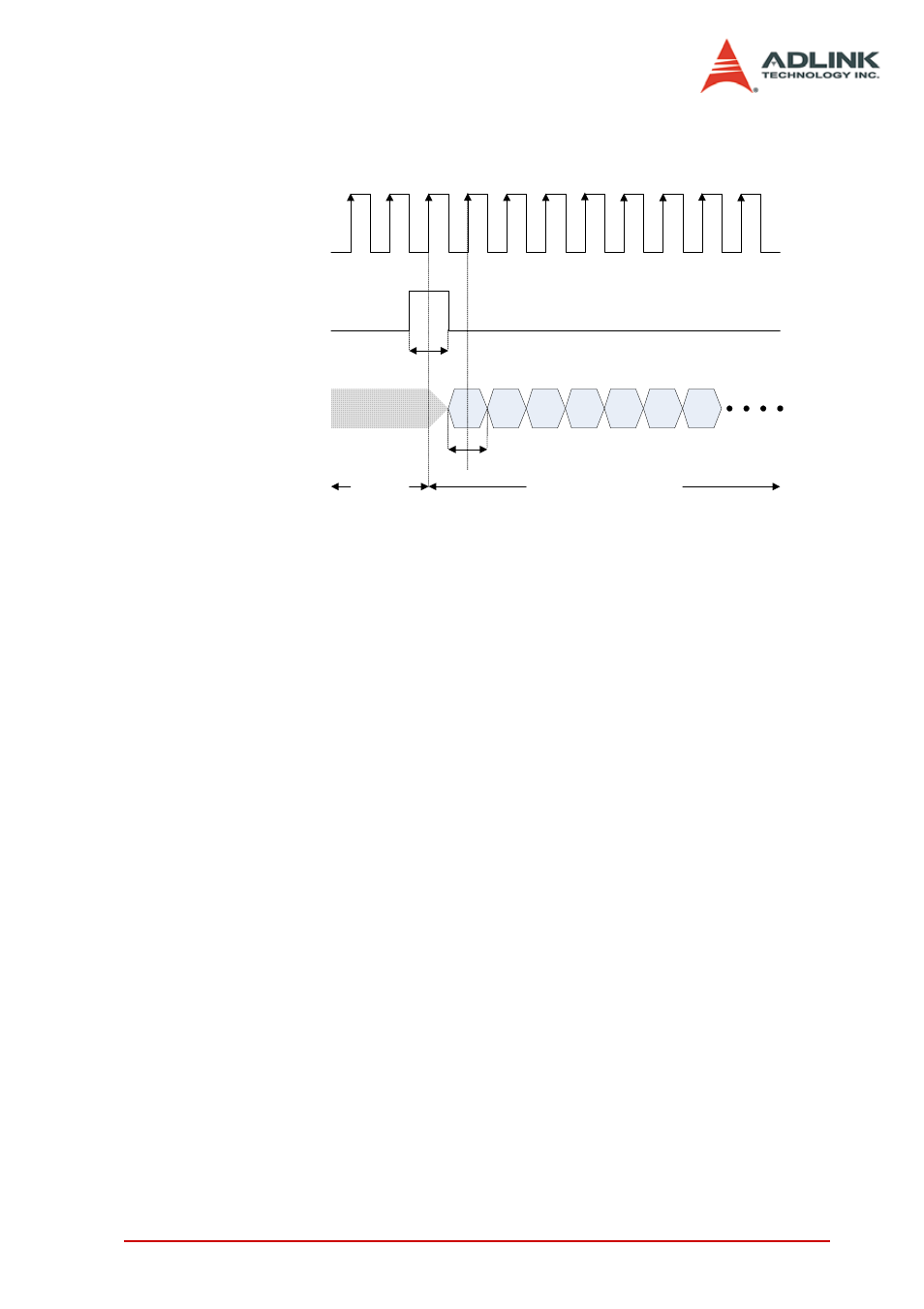

The timing diagram of DI DMA in continuous mode is shown as

below:

Figure 3-11: DI Timing Diagram

Note:

In the continuous mode of DI pattern acquisition, the input

data will be stored in the DI FIFO of the PCIe-7350. The data

then transfer to system memory by bus mastering DMA if

PCIe bus is available. If the speed of translation from exter-

nal device to the DI FIFO on board is higher than that from

DI FIFO to system memory or the PCIe bus is busy for a long

time, the DI FIFO become full and the DI pattern acquisition

controller will stop to write data into DI FIFO until the DI FIFO

is not full. So the data will be lost when the DI FIFO is full.

DO

D1

D2

D3

D4

D5

D6

DI Sampled Clock

Start Trigger

DI Data

Read data into DI FIFO

Wait for

start trigger

t

H

t

SU

t

H

t

SU

t

H

t

SU

= Maximum required setup time

= Maximum required hold time

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (4 pages)

- PCM-6308V+ (52 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)