Introduction 9 – ADLINK PCIe-7350 User Manual

Page 19

Introduction

9

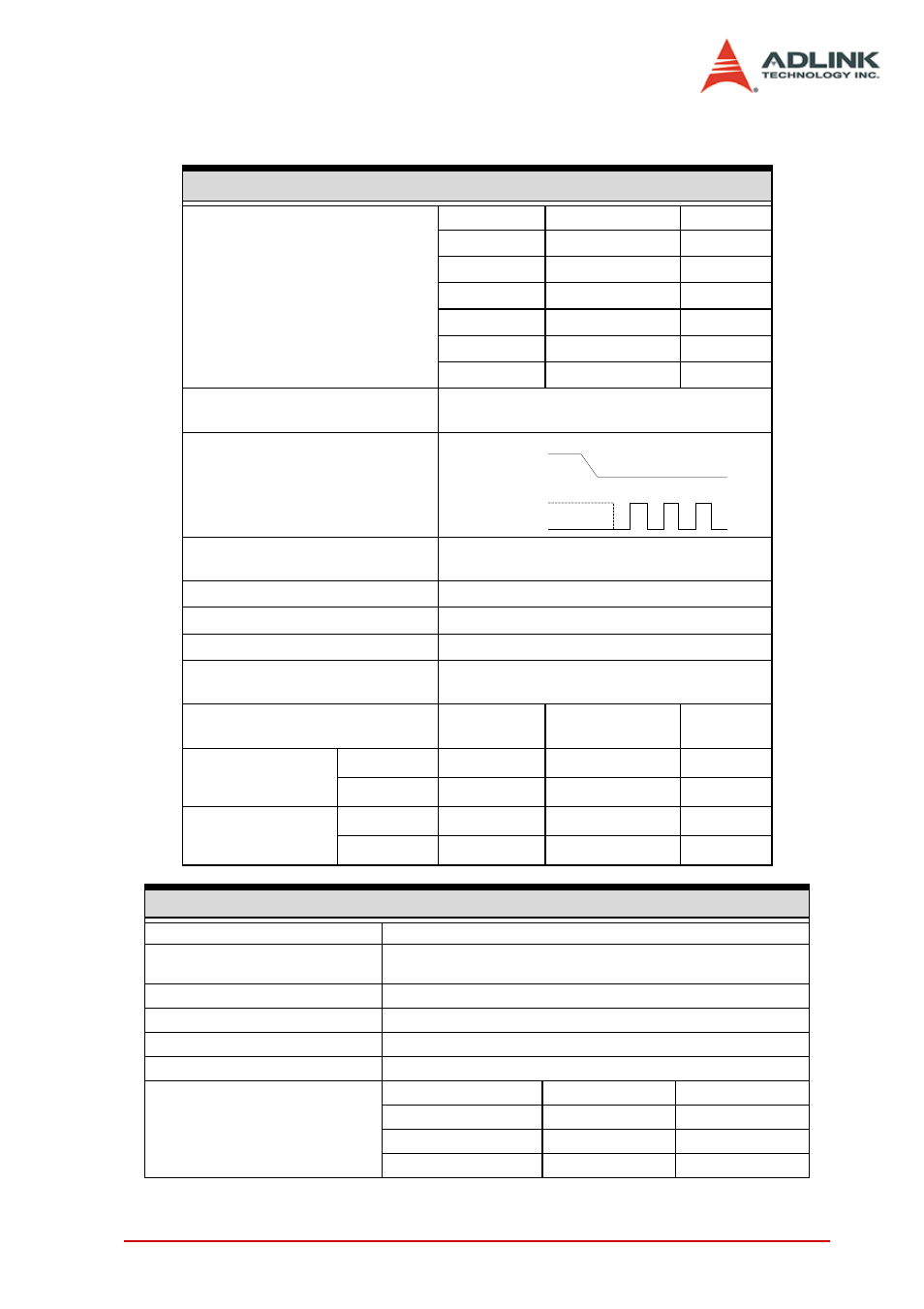

SPI Master Specification

Signal

Direction

Pin

SCK

O

AFI0

SDO

O

AFI1

SDI

I

AFI2

CS_0

O

AFI3

CS_1

O

AFI4

CS_2

O

AFI5

Supported clock rate

(programmable)

244.14 kHz -62.5 MHz,

62.5 MHz / (n + 1); 0 ≤ n ≤ 255

Clock mode

The first bit be transferred

MSB/ LSB

(Default: MSB)

Transfer size of Data

0 - 32 bits

Transfer size of Cmd/ Addr

0 - 32 bits

Dummy size

0 - 15 bits

SPI Slave selection

Max. 3 slave devices

(selected by CS_0 / CS_1 / CS_2

Logic families

(programmable)

1.8 V

2.5 V

3.3 V

Input Voltage

Min. V

IH

1.2 V

1.6 V

2 V

Max. V

IL

0.63 V

0.7 V

0.8 V

Output Voltage

Min. V

OH

1.6 V

2.3 V

3.1 V

Max. V

OL

0.2 V

0.2 V

0.2 V

General Specification

Interface

x1 PCI Express interface

Connector

1. SMB Jack Connector x2 (CLK IN & OUT)

2. 68-pin SCSI-VHDCI x1 (32-bit Data Lines & 8-ch AFI)

Operation Temperature

0°C - 45°C

Storage Temperature

-20°C - 70°C

Humidity

5 - 95%, non-condensing

Dimension

168 mm (L) x 112 mm (H), not including connectors

Power Consumption

Typical

Maximum

+3.3 VDC

450 mA

780 mA

+12V VDC

625 mA

680 mA

Total Power

9 W

10.8 W

CS#

SCK

Mode =1

Mode =0