Introduction, Clock and reset networks overview, Clock resource counts – Achronix Speedster22i Clock and Reset Networks User Manual

Page 4

4

UG027, May 21, 2014

Introduction

Clock and Reset Networks Overview

Speedster22iHD FPGAs have two hierarchical clock networks: a core clock network and a

boundary clock network.

The core clock network is the hierarchical network that feeds resources in the FPGA fabric.

There are two types of core clock networks: a global and a direct. Both of them have common

input sources: Clock input pins and PLL outputs which make up the Clock Generator (CG)

and recovered SerDes input clocks. These input sources get channeled in from both the north

and south sides of the device, and are then fed into the FPGA core through a central trunk.

The boundary clock network is a fully programmable clock network in the IO ring, unique to

Speedster22iHD FPGAs, that provides for significant advantages when clocking IO ring

resources at high frequencies. The boundary clock network is comprised of a low skew global

boundary clock network and a lower jitter local boundary clock network. The inputs to the

boundary clock network are CGs.

Reset signals generated internally or coming from GPIOs are funneled through the Reset

Input Blocks in the device corners into the FPGA core and the IO ring. The IO ring contains a

dedicated reset network but for distribution to core logic, the clock network resources

described above are used.

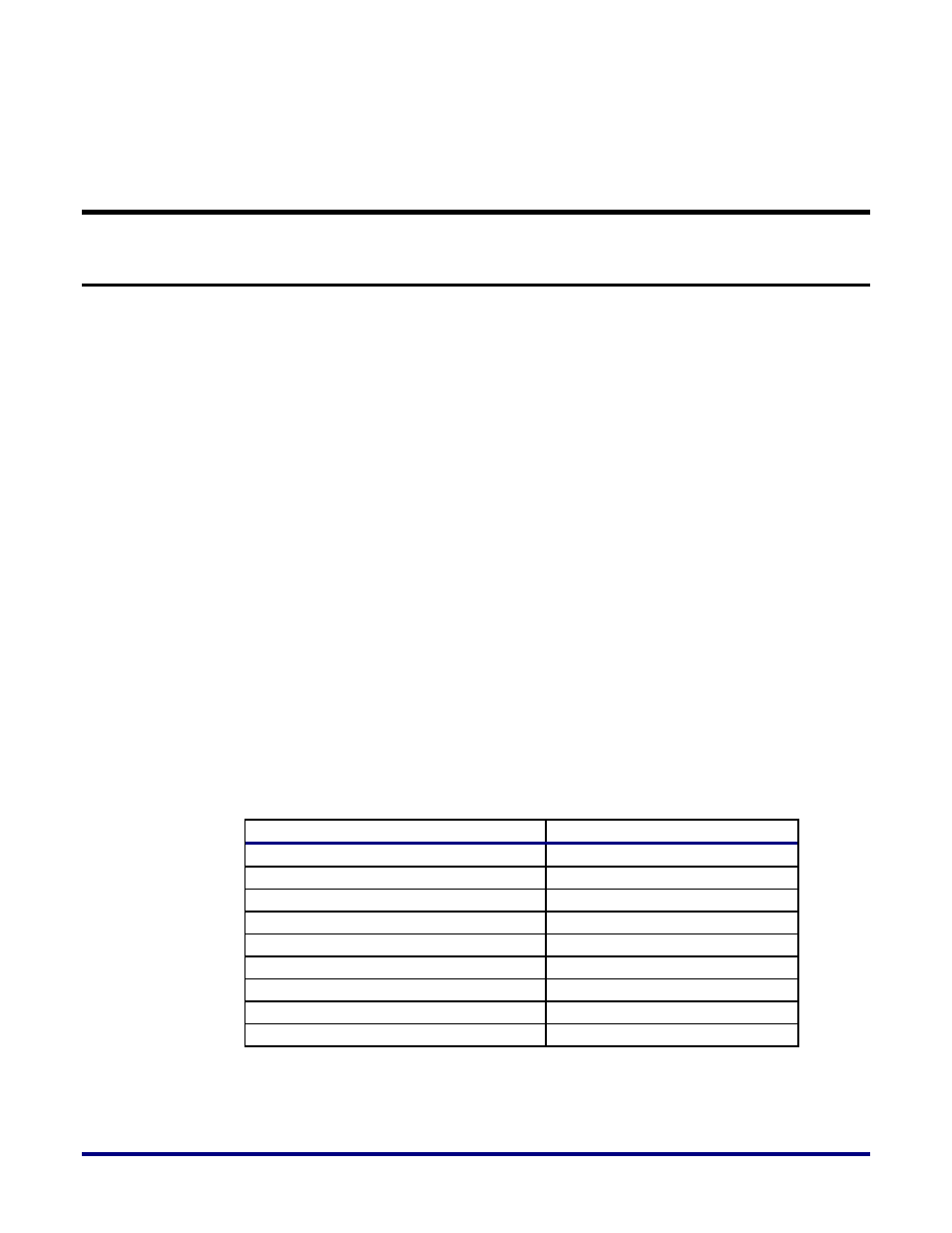

Clock Resource Counts

The following table lists the clock resources available on Speedster22iHD FPGAs.

Table 1: Clock Resource Counts on Speedster22iHD FPGAs

Resource

Number of resources

Clock input pins

24 single ended (12 differential)

Global core clocks

48

Direct core clocks

32

Clocks per IP column in fabric

16

Boundary clocks

16

Global boundary clock hierarchy levels

4

Local boundary clock hierarchy levels

2

Clock generators (CGs)

4 (1 per device corner)

Phase Locked Loops (PLLs)

16 (4 in each CG)