Phase locked loop (pll) – Achronix Speedster22i Clock and Reset Networks User Manual

Page 11

UG027, May 21, 2014

11

Table 3: Snapshot of HD1000 52.5mm package spreadsheet to show clock buffers

Port_Name

DIFF-PAIR

USE

BANK

PURPOSE

CLK/RST USE

pad0_clk_bank_ne

P

C

CB3

USER

CLK RST

pad0_clk_bank_nw

P

C

CB0

USER

CLK RST

pad0_clk_bank_se

P

C

CB2

USER

CLK RST

pad0_clk_bank_sw

P

C

CB1

USER

CLK RST

pad1_clk_bank_ne

N

C

CB3

USER

CLK RST

pad1_clk_bank_nw

N

C

CB0

USER

CLK RST

pad1_clk_bank_se

N

C

CB2

USER

CLK RST

pad1_clk_bank_sw

N

C

CB1

USER

CLK RST

pad2_clk_bank_ne

P

C

CB3

USER

CLK RST

pad2_clk_bank_nw

P

C

CB0

USER

CLK RST

pad2_clk_bank_se

P

C

CB2

USER

CLK RST

pad2_clk_bank_sw

P

C

CB1

USER

CLK RST

pad3_clk_bank_ne

N

C

CB3

USER

CLK RST

pad3_clk_bank_nw

N

C

CB0

USER

CLK RST

pad3_clk_bank_se

N

C

CB2

USER

CLK RST

pad3_clk_bank_sw

N

C

CB1

USER

CLK RST

pad4_clk_bank_ne

P

C

CB3

USER

CLK RST

pad4_clk_bank_nw

P

C

CB0

USER

CLK RST

pad4_clk_bank_se

P

C

CB2

USER

CLK RST

pad4_clk_bank_sw

P

C

CB1

USER

CLK RST

pad5_clk_bank_ne

N

C

CB3

USER

CLK RST

pad5_clk_bank_nw

N

C

CB0

USER

CLK RST

pad5_clk_bank_se

N

C

CB2

USER

CLK RST

pad5_clk_bank_sw

N

C

CB1

USER

CLK RST

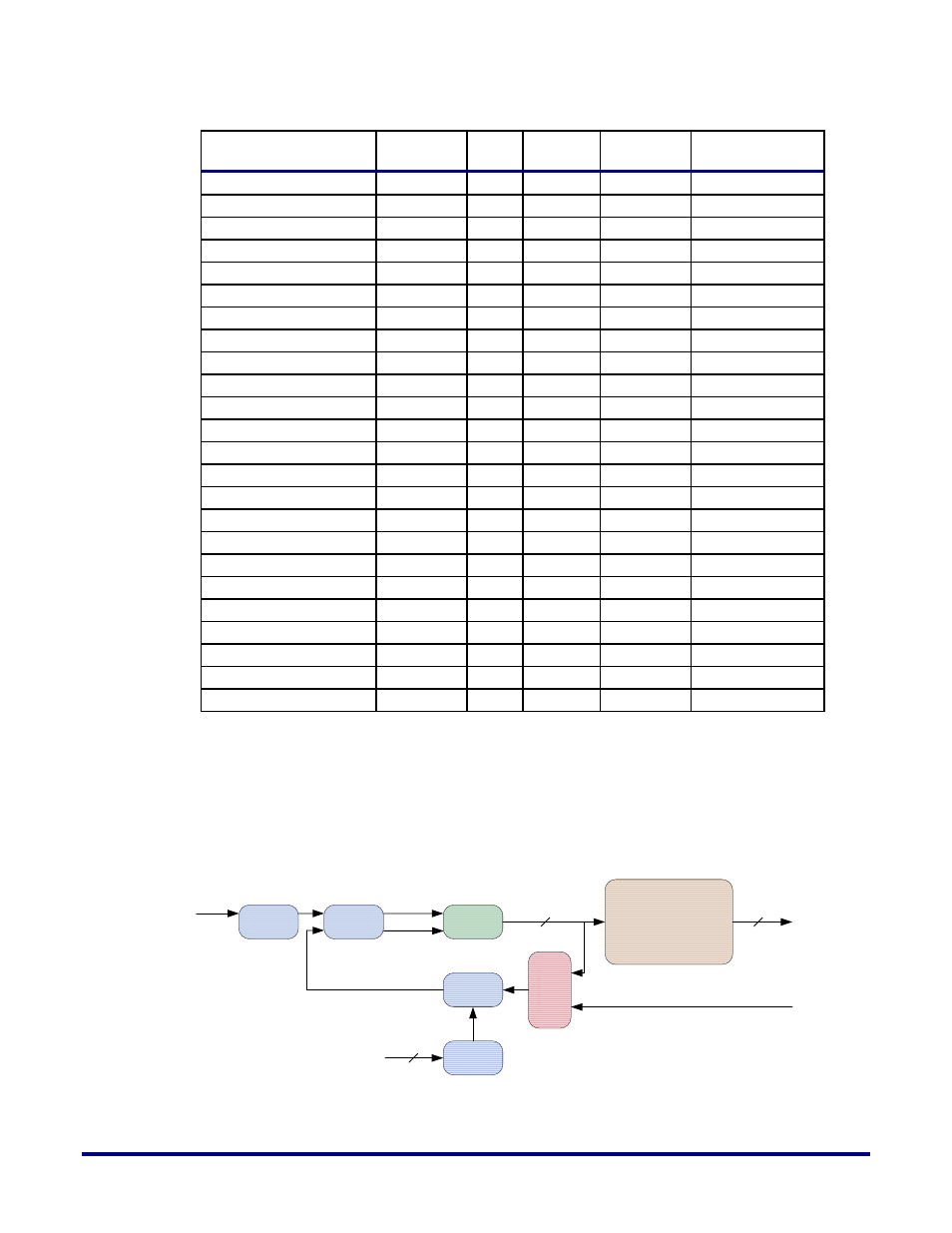

Phase Locked Loop (PLL)

The PLLs are low jitter, wide range, independent multi-phase outputs with glitch-free phase

rotators that can be used for PLL outputs of up to 1066MHz for core circuit applications. The

block diagram below shows a high-level view of the PLL architecture.

Ref Clk

Divider

PFD /

CP / LF

Sigma-

delta

Fbk Clk

Divider

Phase Rotator w/

Divider

Mux

VCO

8-phase

16 bit

4 independent

outputs

Feedback clock

from clock tree

Figure 4: PLL Architecture