Time delay for a/d conversion, Response to slot disable – Rockwell Automation 1746-FIO4V SLC 500 Fast Analog I/O/ User Manual User Manual

Page 37

Publication 1746-UM009B-EN-P - September 2007

Processor and Module Considerations 37

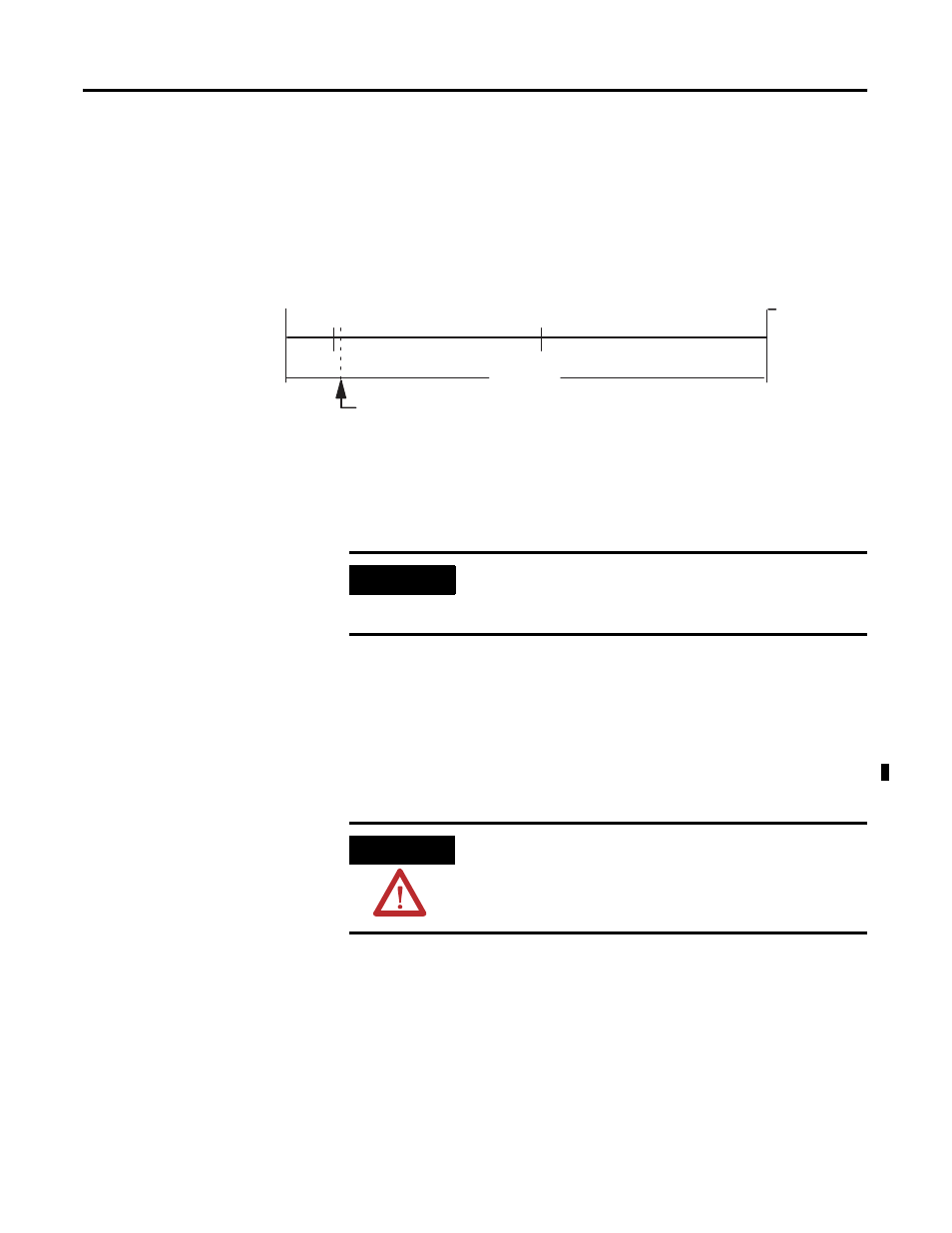

Time Delay for A/D Conversion

The A/D converter uses 7.5 µs for data conversion, 248.5 µs for data

settling, and 256 µs for data transfer to the backplane. New data is

available in 512 µs cycles.

Response Time of A/D Converter

The worst-case specification for the SLC processor to read a step

change is 1.1ms between readings. This is true for a step change

occurring just after data conversion (first 7.5 µs of the 512 µs cycle). In

this case, the read cycle cannot begin until the next data conversion.

Response to Slot Disable

You can disable any I/O rack slot by means of a processor function.

Before disabling a slot containing an analog I/O module, be aware of

the implications.

Data ready for

processor read

Data

conversion

Data

settling

Data transfer to

the backplane

Start

7.5 µs

248.5 µs

256 µs

512 µs

Worst case point for a change of input to occur.

This results in a 1.1ms delay for the processor to read a step change.

IMPORTANT

Do not attempt to read data from the module more often than

once every 512 µs. If you do, the module may not be able to

update new data.

ATTENTION

Clearly understand the safety implications of disabling an

analog module slot before doing it.