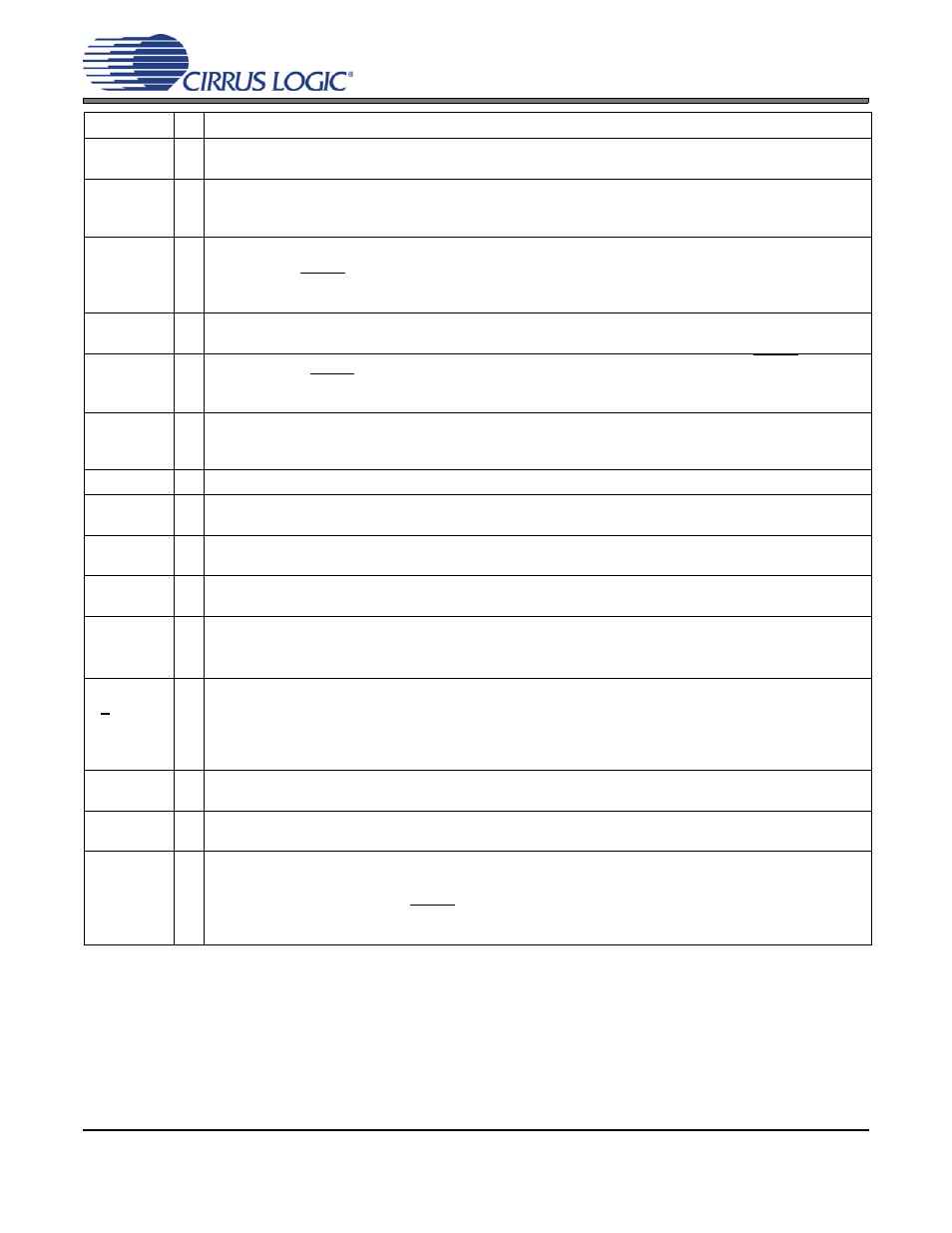

Cs8415a – Cirrus Logic CS8415A User Manual

Page 34

34

DS470F4

CS8415A

RMCK

10

Recovered Master Clock (Output) - Recovered master clock output when PLL is locked to the incoming

AES3 stream. Frequency is 256x the sample rate (Fs).

RERR

11

Receiver Error (Output) - When high, indicates an error condition in the AES3 receiver. The status of this

pin is updated once per sub-frame of incoming AES3 data. Conditions that can cause RERR to go high are:

validity bit high, parity error, bi-phase coding error, and loss of lock by the PLL.

RCBL

12

Receiver Channel Status Block (Output) -Indicates the beginning of a received channel status block.

RCBL goes high two frames after the reception of a Z preamble, remains high for 16 frames while COPY,

ORIG, AUDIO,

EMPH

and PRO are updated, and returns low for the remainder of the block. RCBL

changes on rising edges of RMCK.

PRO

13

PRO Channel Status Bit (Output) - Reflects the state of the Professional/Consumer Channel Status bit in

the incoming AES3 data stream. Low indicates Consumer and high indicates Professional.

CHS

14

Channel Select (Input) - Selects which sub-frame’s channel status data is output on the

EMPH

, COPY,

ORIG, PRO and AUDIO pins. Channel A is selected when CHS is low, channel B is selected when CHS is

high.

NVERR

15

No Validity Receiver Error Indicator (Output) - A high output indicates a problem with the operation of the

AES3 receiver. The status of this pin is updated once per frame of incoming AES3 data. Conditions that

cause NVERR to go high are: parity error, and bi-phase coding error, and loss of lock by the PLL.

OSCLK

16

Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin.

OLRCK

17

Serial Audio Output Left/Right Clock (Input/Output) - Word rate clock for the audio data on the SDOUT

pin. Frequency will be the output sample rate (Fs).

SDOUT

18

Serial Audio Output Data (Output) - Audio data serial output pin. This pin is also a start-up option which

determines if the serial audio port is master or slave. A 47 k

Ω resistor to either VL+ or DGND is required.

AUDIO

19

Audio Channel Status Bit (Output) - Reflects the state of the audio/non audio Channel Status

bit in the incoming AES3 data stream. When this bit is low a valid audio stream is indicated.

DGND3

DGND2

DGND

20

21

22

Digital Ground (Input) - Ground for the digital circuitry in the chip. DGND and AGND should be connected

to a common ground area under the chip.

H/S

24

Hardware/Software Mode Control (Input) - Determines the method of controlling the operation of the

CS8415A, and the method of accessing CS and U data. In software mode, device control and CS and U

data access is primarily through the control port, using a microcontroller. Hardware mode provides an alter-

nate mode of operation and access to the CS and U data through dedicated pins.

This pin should be perma-

nently tied to VL+ or DGND.

U

25

User Data (Output) - Outputs user data from the AES3 receiver, clocked by the rising and falling edges of

OLRCK.

C

26

Channel Status Data (Output) - Outputs channel status data from the AES3 receiver, clocked by the rising

and falling edges of OLRCK.

ORIG

28

Original Channel Status (Output) - SCMS generation indicator. This is decoded from the incoming cate-

gory code and the L bit in the Channel Status bits. A low output indicates that the source of the audio data

stream is a copy not an original. A high indicates that the audio data stream is original. This pin is also a

start-up option which, along with

EMPH

, determines the serial audio port format. A 47 k

Ω resistor to either

VL+ or DGND is required.

Pin Name

# Pin Description