Cs8415a – Cirrus Logic CS8415A User Manual

Page 31

DS470F4

31

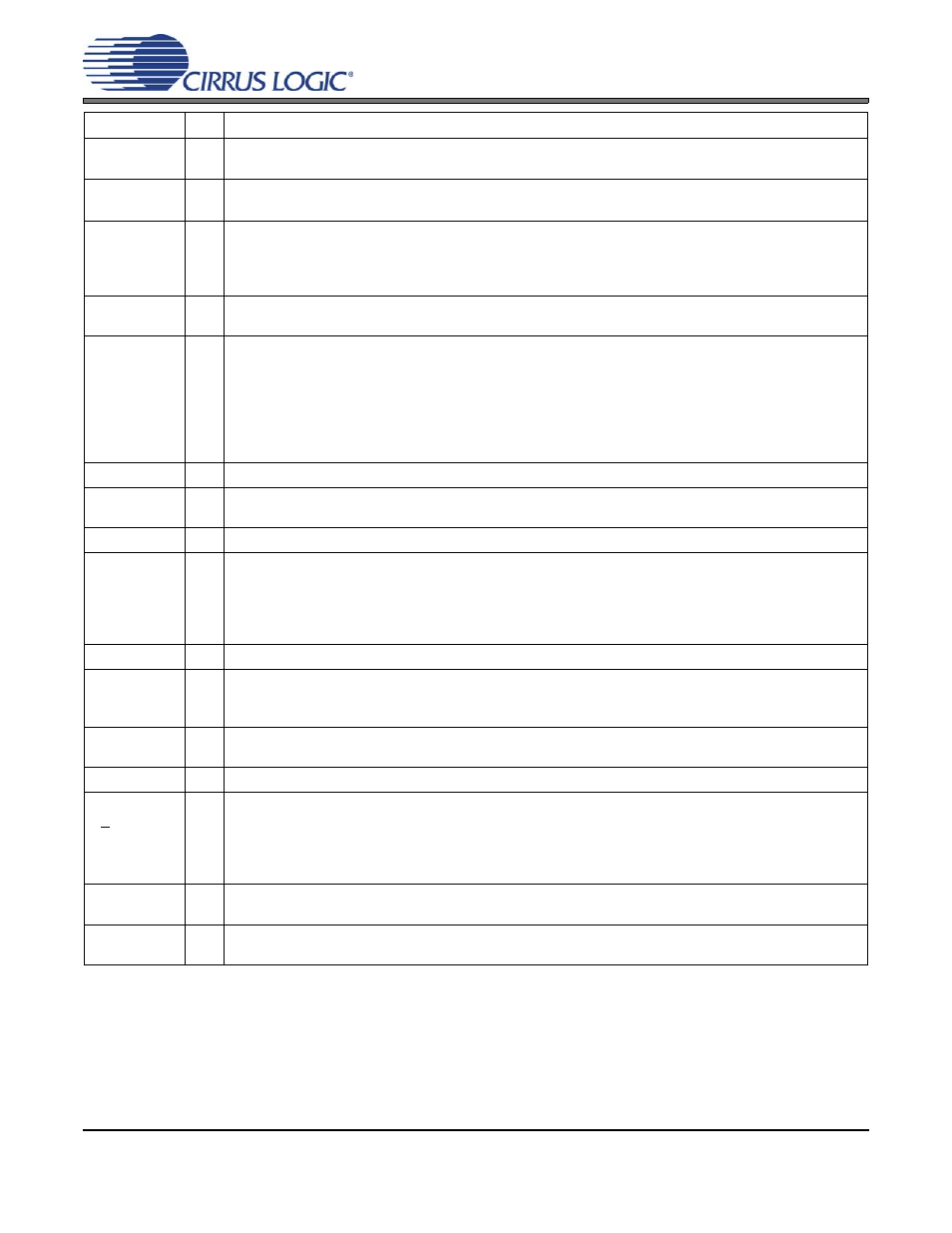

CS8415A

AGND

7

Analog Ground (Input) - Ground for the analog circuitry in the chip. AGND and DGND should be con-

nected to a common ground area under the chip.

FILT

8

PLL Loop Filter (Output) - An RC network should be connected between this pin and ground. See

“Appendix C: PLL Filter” on page 41

for recommended schematic and component values.

RST

9

Reset (Input) - When RST is low, the CS8415A enters a low power mode and all internal states are

reset. On initial power up, RST must be held low until the power supply is stable, and all input clocks are

stable in frequency and phase. This is particularly true in hardware mode with multiple CS8415A

devices where synchronization between devices is important

RMCK

10

Input Section Recovered Master Clock (Output) - Input section recovered master clock output when

PLL is used. Frequency defaults to 256x the sample rate (Fs) and may be set to 128x.

RERR

11

Receiver Error (Output) - When high, indicates a problem with the operation of the AES3 receiver. The

status of this pin is updated once per sub-frame of incoming AES3 data. Conditions that can cause

RERR to go high are: validity, parity error, bi-phase coding error, confidence, QCRC and CCRC errors,

as well as loss of lock in the PLL. Each condition may be optionally masked from affecting the RERR pin

using the Receiver Error Mask Register. The RERR pin tracks the status of the unmasked errors: the pin

goes high as soon as an unmasked error occurs and goes low immediately when all unmasked errors

go away.

OSCLK

16

Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin

OLRCK

17

Serial Audio Output Left/Right Clock (Input/Output) - Word rate clock for the audio data on the

SDOUT pin. Frequency will be the output sample rate (Fs)

SDOUT

18

Serial Audio Output Data (Output) - Audio data serial output pin

INT

19

Interrupt (Output) - Indicates errors and key events during the operation of the CS8415A. All bits affect-

ing INT may be unmasked through bits in the control registers. The condition(s) that initiated interrupt

are readable through a control register. The polarity of the INT output, as well as selection of a standard

or open drain output, is set through a control register. Once set true, the INT pin goes false only after the

interrupt status registers have been read and the interrupt status bits have returned to zero

U

20

User Data (Output) - Outputs User data from the AES3 receiver, see

for timing information

OMCK

21

System Clock (Input) - When the OMCK System Clock Mode is enabled using the SWCLK bit in the

Control 1 register, the clock signal input on this pin is output through RMCK. OMCK serves as reference

signal for OMCK/RMCK ratio expressed in register 1Eh

DGND

22

Digital Ground (Input) - Ground for the digital circuitry in the chip. DGND and AGND should be con-

nected to a common ground area under the chip.

VL+

23

Positive Digital Power (Input) - Positive supply for the digital section. Typically +3.3 V or +5.0 V.

H/S

24

Hardware/Software Mode Control (Input) - Determines the method of controlling the operation of the

CS8415A, and the method of accessing CS and U data. In software mode, device control and CS and U

data access is primarily through the control port, using a microcontroller. Hardware mode provides an

alternate mode of operation and access to the CS and U data through dedicated pins.

This pin should

be permanently tied to VL+ or DGND

AD1/CDIN

27

Address Bit 1 (I²C) / Serial Control Data in (SPI) (Input) - In I²C mode, AD1 is a chip address pin. In

SPI mode, CDIN is the input data line for the control port interface

SCL/CCLK

28

Control Port Clock (Input) - Serial control interface clock and is used to clock control data bits into and

out of the CS8415A. In I²C mode, SCL requires an external pull-up resistor to VL+

Pin Name

#

Pin Description