1 aes3 channel status(c) bit management, Figure 17. channel status data buffer structure, 1 accessing the e buffer – Cirrus Logic CS8406 User Manual

Page 36: Appendix b: channel status and user

36

DS580F6

CS8406

16.APPENDIX B: CHANNEL STATUS AND USER DATA BUFFER

MANAGEMENT

The CS8406 has a comprehensive channel status (C) and user (U) data buffering scheme which allows the user to

manage the C and U data through the control port.

16.1 AES3 Channel Status(C) Bit Management

The CS8406 contains sufficient RAM to store a full block of C data for both A and B channels (192x2 = 384

bits), and also 384 bits of U information. The user may read from or write to these RAM buffers through the

control port.

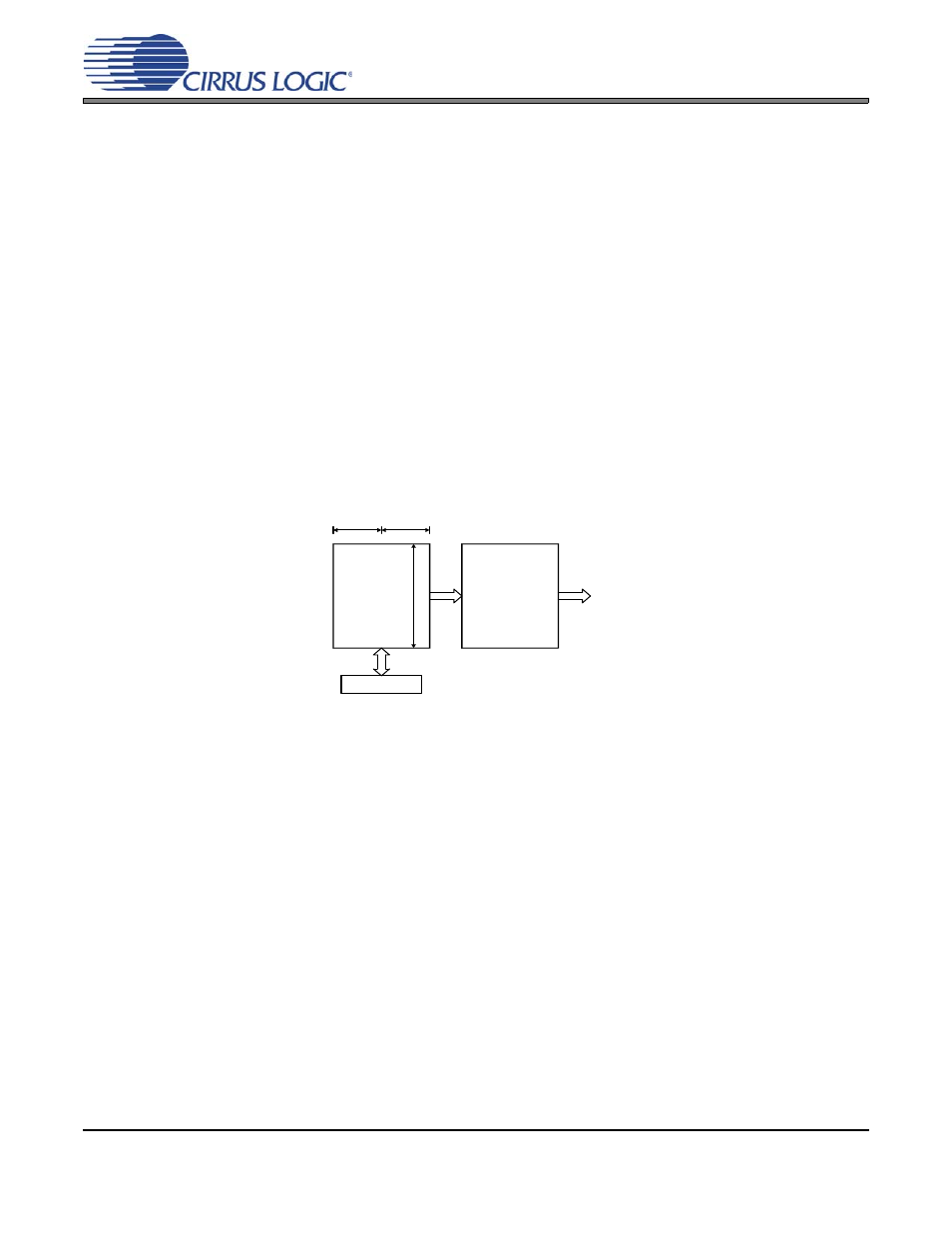

The CS8406 manages the flow of channel status data at the block level, meaning that entire blocks of chan-

nel status information are buffered at the input, synchronized to the output timebase, and then transmitted.

The buffering scheme involves a cascade of 2 block-sized buffers, named E and F, as shown in

.

The MSB of each byte represents the first bit in the serial C data stream. For example, the MSB of byte 0

(which is at control port address 20h) is the consumer/professional bit for channel status block A.

The E buffer is accessible from the control port, allowing read and writing of the C data. The F buffer is used

as the source of C data for the AES3 transmitter. The F buffer accepts block transfers from the E buffer.

16.1.1

Accessing the E buffer

The user can monitor the data being transferred by reading the E buffer, which is mapped into the register

space of the CS8406, through the control port. The user can modify the data to be transmitted by writing

to the E buffer.

The user can configure the interrupt enable register to cause interrupts to occur whenever “E to F” buffer

transfers occur. This allows determination of the allowable time periods to interact with the E buffer.

Also provided is an “E to F” inhibit bit. The “E to F” buffer transfer is disabled whenever the user sets this

bit. This may be used whenever “long” control port interactions are occurring.

A flowchart for reading and writing to the E buffer is shown in

. For writing, the sequence starts

after a E to F transfer, which is based on the output timebase.

If the channel status block to transmit indicates PRO Mode, then the CRCC byte is automatically calcu-

lated by the CS8406, and does not have to be written into the last byte of the block by the host microcon-

Control Port

To

AES3

Transm itter

E

24

words

8-bits

8-bits

A

B

F

Transm it

Data

Buffer

Figure 17. Channel Status Data Buffer Structure