7 interrupt 1 status (07h) (read only), 8 interrupt 2 status (08h) (read only), 9 interrupt 1 mask (09h) – Cirrus Logic CS8406 User Manual

Page 22: Cs8406

22

DS580F6

CS8406

8.7

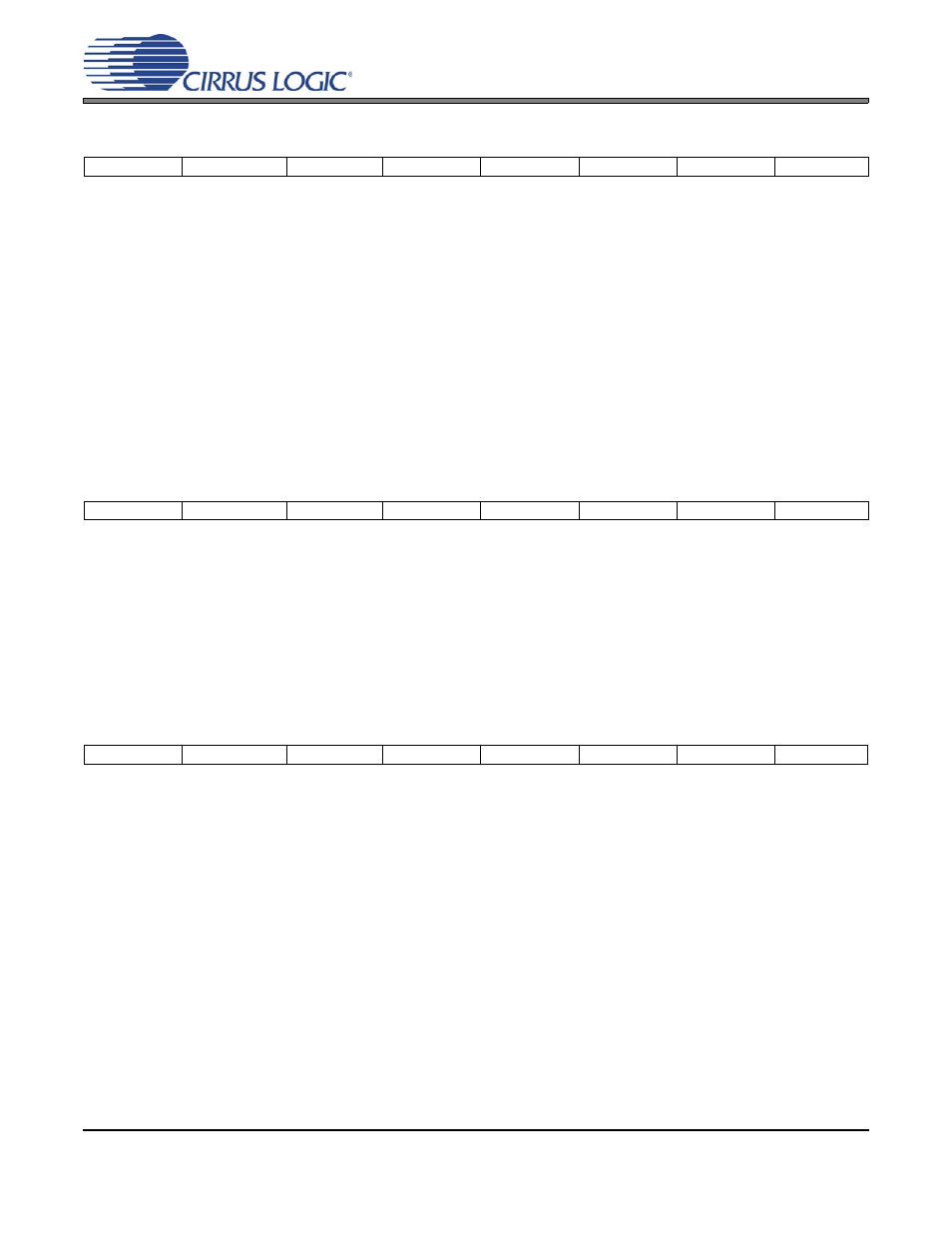

Interrupt 1 Status (07h) (Read Only)

For all bits in this register, a ‘1’ means the associated interrupt condition has occurred at least once since

the register was last read. A ‘0’ me ans the associated interrupt condition has NOT occurred since the last

reading of the register. Reading the register resets all bits to ‘0’, unless the Interrupt Mode is set to level and

the interrupt source is still true. Status bits that are masked off in the associated mask register will always

be ‘0’ in this register. This register defaults to 00h.

TSLIP - AES3 transmitter source data slip interrupt

In data flows where OMCK, which clocks the AES3 transmitter, is asynchronous to the data source, this bit

will go high every time a data sample is dropped or repeated. When TCBL is an input, this bit will go high

on receipt of a new TCBL signal.

EFTC - E to F C-buffer transfer interrupt. The source for this bit is true during the E to F buffer transfer in

the C bit buffer management process.

8.8

Interrupt 2 Status (08h) (Read Only)

For all bits in this register, a ‘1’ means the associated interrupt condition has occurred at least once since

the register was last read. A ‘0’ me ans the associated interrupt condition has NOT occurred since the last

reading of the register. Reading the register resets all bits to ‘0’, unless the Interrupt Mode is set to level and

the interrupt source is still true. Status bits that are masked off in the associated mask register will always

be ‘0’ in this register. This register defaults to 00h.

EFTU - E to F U-buffer transfer interrupt. (Block Mode only) The source of this bit is true during the E to F

buffer transfer in the U bit buffer management process.

8.9

Interrupt 1 Mask (09h)

The bits of this register serve as a mask for the Interrupt 1 register. If a mask bit is set to 1, the error is un-

masked, meaning that its occurrence will affect the INT pin and the status register. If a mask bit is set to 0,

the error is mas ked, meaning that its occurrence will not affect the INT pin or the status register. The bit

positions align with the corresponding bits in Interrupt 1 register. This register defaults to 00h.

7

6

5

4

3

2

1

0

TSLIP

0

0

0

0

0

EFTC

0

7

6

5

4

3

2

1

0

0

0

0

0

0

EFTU

0

0

7

6

5

4

3

2

1

0

TSLIPM

0

0

0

0

0

EFTCM

0