Control port register summary, Table 1. control register map summary – Cirrus Logic CS8406 User Manual

Page 18

18

DS580F6

CS8406

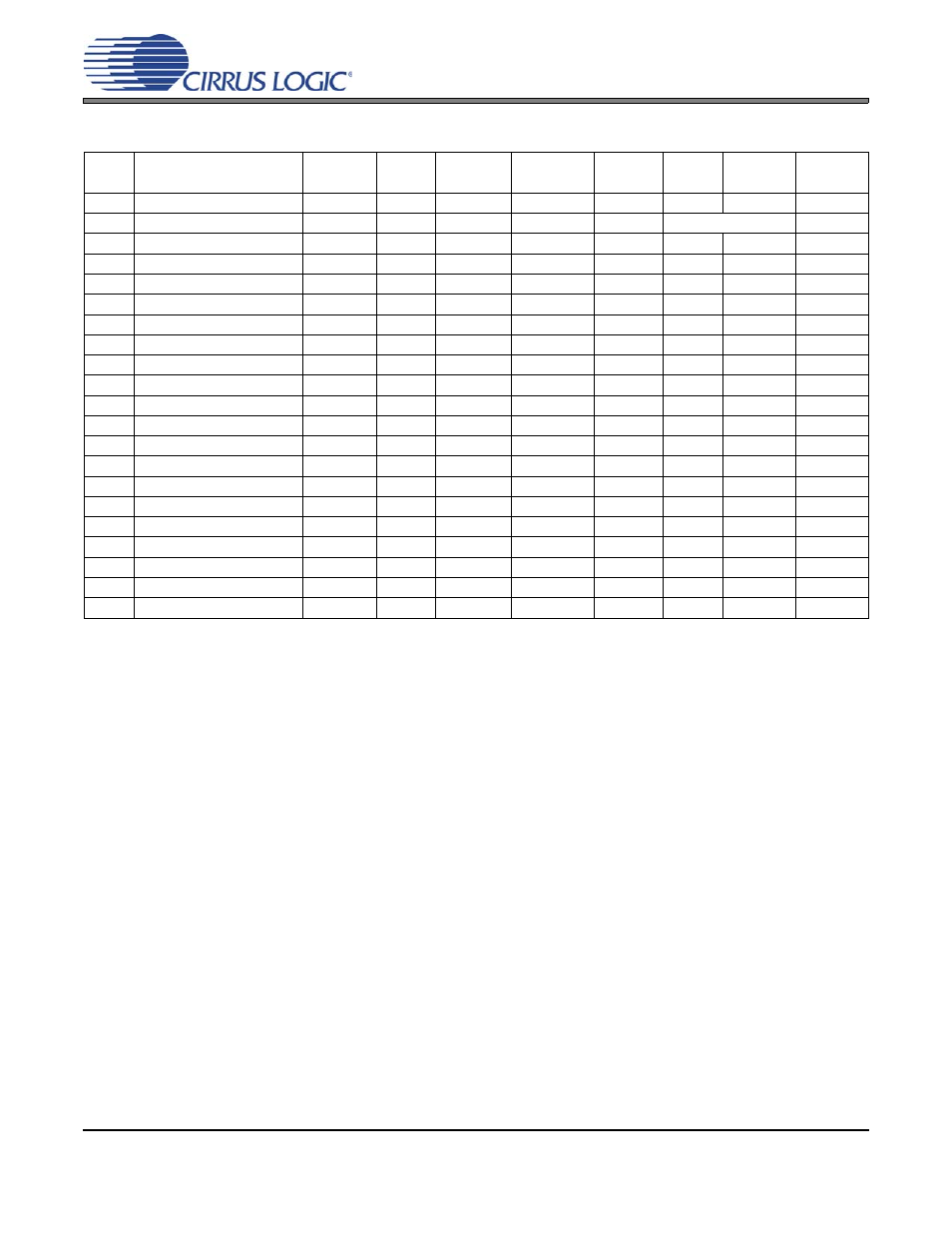

7. CONTROL PORT REGISTER SUMMARY

Note: Reserved registers must not be written to during normal operation. Some reserved registers are used for

test modes, which can completely alter the normal operation of the CS8406.

Addr

(HEX)

Function

7

6

5

4

3

2

1

0

00 Reserved

0

0

0

0

0

0

0

0

01 Control 1

0

VSET

0

MUTEAES

0

INT1

INT0

TCBLD

02 Control 2

0

0

0

0

0

MMT MMCST MMTLR

03 Data Flow Control

0

TXOFF AESBP

0

0

0

0

0

04 Clock Source Control

0

RUN

CLK1

CLK0

0

0

0

0

05 Serial Input Format

SIMS

SISF

SIRES1

SIRES0

SIJUST SIDEL SISPOL SILRPOL

06 Reserved

0

0

0

0

0

0

0

0

07 Interrupt 1 Status

TSLIP

0

0

0

0

0

EFTC

0

08 Interrupt 2 Status

0

0

0

0

0

EFTU

0

0

09 Interrupt 1 Mask

TSLIPM

0

0

0

0

0

EFTCM

0

0A Interrupt 1 Mode (MSB) TSLIP1

0

0

0

0

0

EFTC1

0

0B Interrupt 1 Mode (LSB) TSLIP0

0

0

0

0

0

EFTC0

0

0C Interrupt 2 Mask

0

0

0

0

0

EFTUM

0

0

0D Interrupt 2 Mode (MSB)

0

0

0

0

0

EFTU1

0

0

0E Interrupt 2 Mode (LSB)

0

0

0

0

0

EFTU0

0

0

0F-11 Reserved

0

0

0

0

0

0

0

0

12 CS Data Buffer Control

0

0

BSEL

0

0

EFTCI

CAM

0

13 U Data Buffer Control

0

0

0

UD

UBM1

UBM0

0

EFTUI

1D-1F Reserved

0

0

0

0

0

0

0

0

20-37 C or U Data Buffer

7F ID and Version

ID3

ID2

ID1

ID0

VER3

VER2

VER1

VER0

Table 1. Control Register Map Summary