Figures 8, Cs8406 – Cirrus Logic CS8406 User Manual

Page 14

14

DS580F6

CS8406

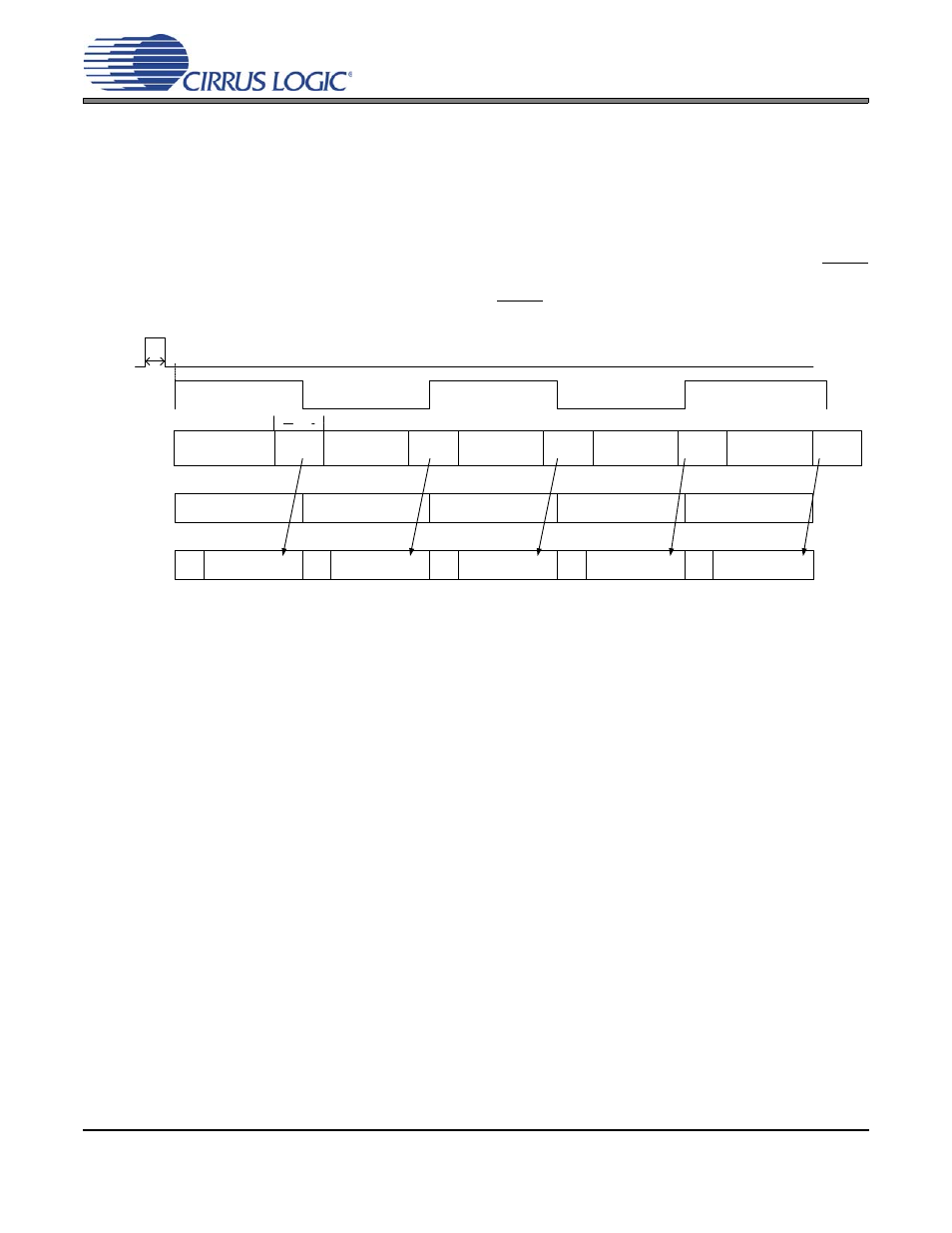

a) With TCBL set to input, driving TCBL high for >3 OMCK clocks will cause a frame start, as well as a new

channel status block start.

b) If the serial audio input port is in Slave Mode and TCBL is set to output, the start of the A channel sub-

frame will be aligned with the leading edge of ILRCK.

The timing of TCBL, VLRCK, C, U, and V are illustrated in

and

. VLRCK is the internal vir-

tual word clock signal, and is used here only to illustrate the timing of the C, U, and V bits. In Stereo Mode

VLRCK = AES3 frame rate and in Mono Mode VLRCK = 2 x AES3 frame rate. If the serial audio input port

is set to Slave Mode and TCBL is an output, VLRCK = ILRCK when SILRPOL = 0 and VLRCK = ILRCK

when SILRPOL = 1. If the serial audio input port is set to master mode and TCBL is a n input,

VLRCK = ILRCK when SILRPOL = 0 and VLRCK = ILRCK when SILRPOL = 1.

VCU[0]

VCU[1]

VCU[2]

VCU[3]

VCU[4]

VLRCK

V/C/U

Data [4]

Data [5]

Data [6]

Data [7]

Data [8]

SDIN

Data [0]

Data [1]

Data [2]

Data [3]

Data [4]

TXP(N)

Z

Y

X

Y

X

Tsetup

Thold

Tth

TCBL

Figure 8. AES3 Transmitter Timing for C, U, and V Pin Input Data, Stereo Mode

Note:

1. T

setup

15% AES3 frame rate

2. T

hold

= 0

3. T

th

> 3 OMCKS if TCBL is an input