Switching characteristics - t1 clock/data, Switching characteristics - e1 clock/data – Cirrus Logic CS61583 User Manual

Page 6

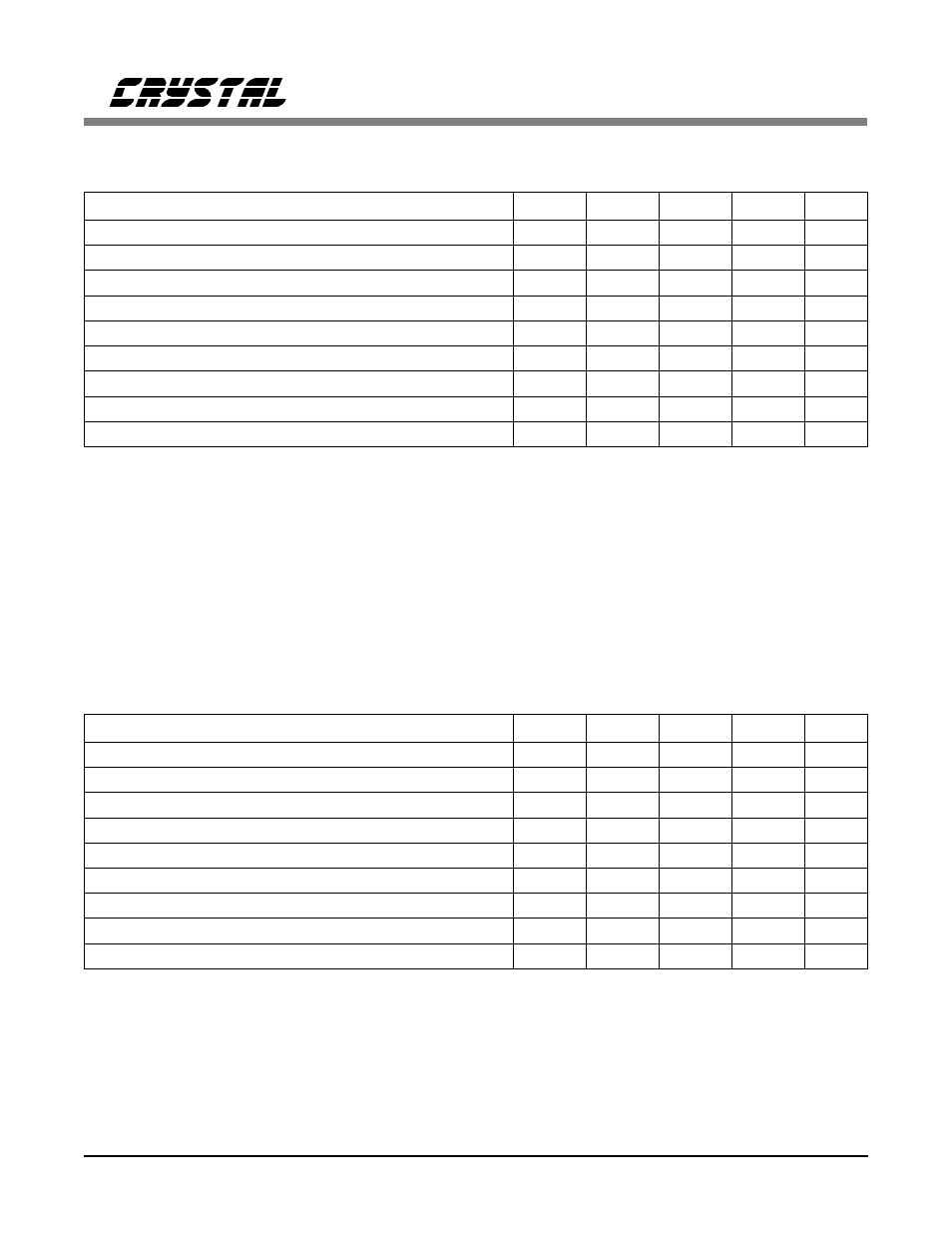

SWITCHING CHARACTERISTICS - T1 CLOCK/DATA

(T

A

= -40 to 85 °C; power supply

pins within

±

5% of nominal; Inputs: Logic 0 = 0V, Logic 1 = DV+) (See Figures 1, 2, and 3)

Parameter

Symbol

Min

Typ

Max

Units

TCLK Frequency

(Note 25)

f

tclk

-

1.544

-

MHz

TCLK Duty Cycle

t

pwh2

/t

pw2

30

50

70

%

RCLK Duty Cycle

(Note 26) t

pwh1

/t

pw1

45

50

55

%

Rise Time (All Digital Outputs)

(Note 27)

t

r

-

-

65

ns

Fall Time (All Digital Outputs)

(Note 27)

t

f

-

-

65

ns

RPOS/RNEG (RDATA) to RCLK Rising Setup Time

t

su1

-

274

-

ns

RCLK Rising to RPOS/RNEG (RDATA) Hold Time

t

h1

-

274

-

ns

TPOS/TNEG (TDATA) to TCLK Falling Setup Time

t

su2

25

-

-

ns

TCLK Falling to TPOS/TNEG (TDATA) Hold Time

t

h2

25

-

-

ns

Notes: 25. The maximum burst rate of a gapped TCLK input clock is 8.192 MHz. For the gapped clock to be

tolerated by the CS61583, the jitter attenuator must be switched to the transmit path of the line

interface. The maximum gap size that can be tolerated on TCLK is 28 UIp-p.

26. RCLK duty cycle may be outside the specified limits when the jitter attenuator is in the receive path,

and when the jitter attenuator is employing the overflow/underflow protection mechanism.

27. At max load of 50 pF.

SWITCHING CHARACTERISTICS - E1 CLOCK/DATA

(T

A

= -40 to 85 °C; power supply

pins within

±

5% of nominal; Inputs: Logic 0 = 0V, Logic 1 = DV+) (See Figures 1, 2, and 3)

Parameter

Symbol

Min

Typ

Max

Units

TCLK Frequency

(Note 25)

f

tclk

-

2.048

-

MHz

TCLK Duty Cycle

t

pwh2

/t

pw2

30

50

70

%

RCLK Duty Cycle

(Note 26) t

pwh1

/t

pw1

45

50

55

%

Rise Time (All Digital Outputs)

(Note 27)

t

r

-

-

65

ns

Fall Time (All Digital Outputs)

(Note 27)

t

f

-

-

65

ns

RPOS/RNEG (RDATA) to RCLK Rising Setup Time

t

su1

-

194

-

ns

RCLK Rising to RPOS/RNEG (RDATA) Hold Time

t

h1

-

194

-

ns

TPOS/TNEG (TDATA) to TCLK Falling Setup Time

t

su2

25

-

-

ns

TCLK Falling to TPOS/TNEG (TDATA) Hold Time

t

h2

25

-

-

ns

CS61583

6

DS172PP5