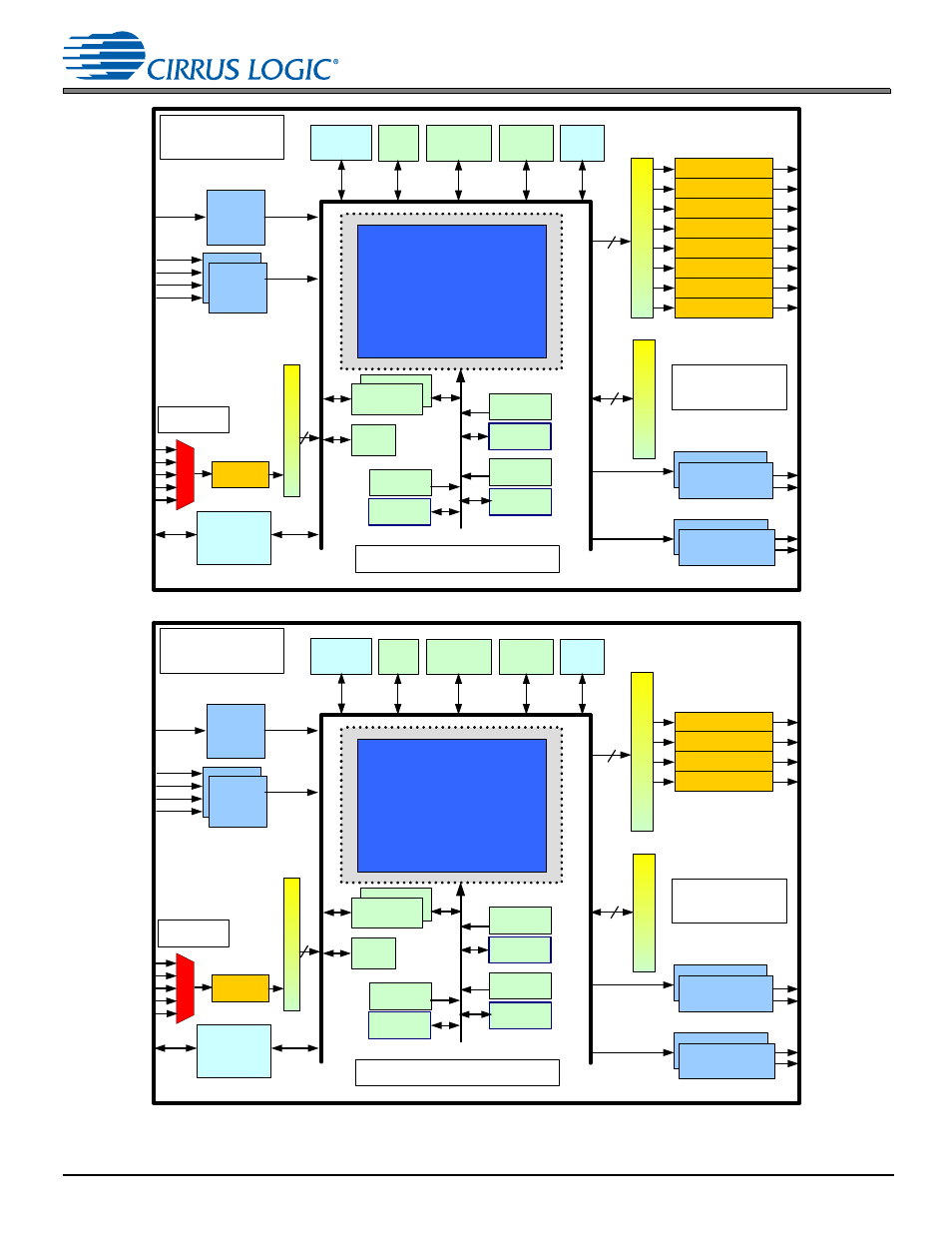

Fig. 4-2, Fig. 4-3, Bit core – Cirrus Logic CS470xx User Manual

Page 8: 4 hardware functional description

DS787PP9

8

4 Hardware Functional Description

Figure 4-2. CS47028 Top-level Block Diagram

Figure 4-3. CS47024 Top-level Block Diagram

x8

x4

x2

x2

DAC0

text

32-bit Core

in the CS 47028 DSP

DMA

SPI / I

2

C

Control

I

2

S

I

2

S

I

2

S / S/PDIF

PLL

ROM

S

R

C

2

P

e

ri

p

h

er

al

B

u

s

Clock

Manager

Timers

RAM

X

GPIO

DAC1

DAC2

DAC3

DAC4

DAC5

DAC6

DAC7

MU

X

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-bit SRAM with three 2K blocks

Assignable to Program or Y Data memory

Me

m

o

ry

B

u

s

I

2

S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/3

DBC

(I

2

C Slave)

PIC

ADC’s & DAC’s operate

in Single ended or

Differential mode

S

R

C

3

8ch

8ch

SRC3 has 8

independent Channels

for In or Out

4ch

x8

x4

x2

x2

text

32-bit Core

in the CS 47024 DSP

DMA

SPI / I

2

C

Control

I

2

S

I

2

S

I

2

S / S/PDIF

PLL

ROM

S

R

C

2

P

e

ri

p

h

er

al

B

u

s

Clock

Manager

Timers

RAM

X

GPIO

DAC0

DAC1

DAC2

DAC3

MU

X

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-bit SRAM with three 2K blocks

Assignable to Program or Y Data memory

Me

m

o

ry

B

u

s

I

2

S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/3

DBC

(I

2

C Slave)

PIC

ADC’s & DAC’s operate

in Single ended or

Differential mode

S

R

C

3

8ch

8ch

SRC3 has 8

independent Channels

for In or Out

4ch