Lineup/features – GW Instek SFG-2000 Series User Manual

Page 6

GETTING

STARTED

11

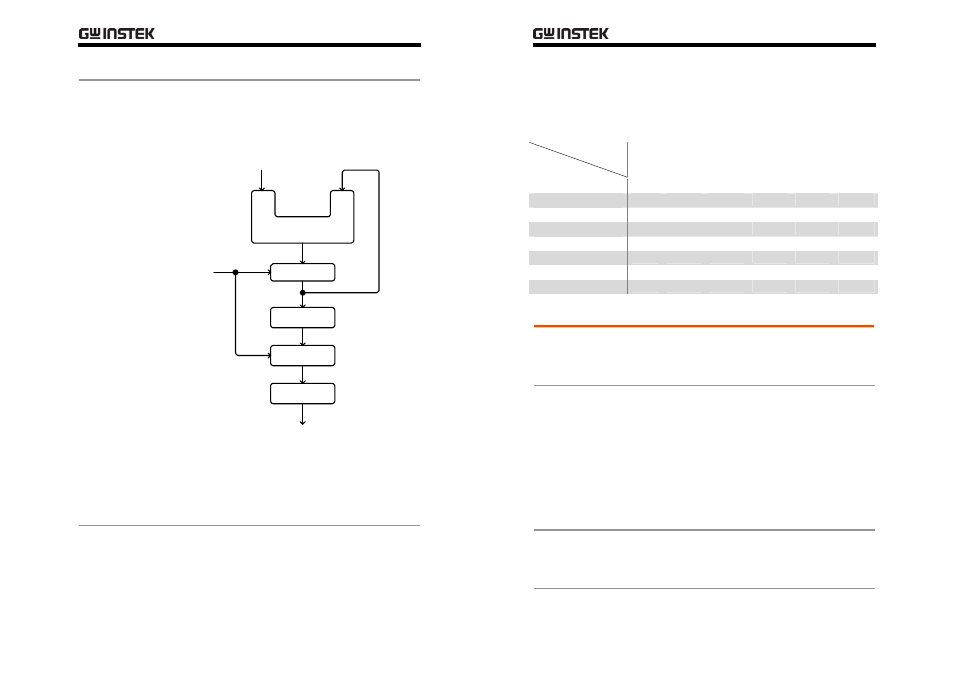

Block diagram

DDS synthesizer consists of Phase accumulator

(counter), lookout table data (ROM), Digital-to-analog

converter (DAC), and Low-pass filter (LPF).

Frequency

Control Word (K)

28bit

Phase

Accumulator

28bit

Register

Table

ROM/RAM

Digital-Analog

Converter

Low-Pass

Filter

System Clock

(fs)

Output (fo)

28bit

12bit

The phase accumulator adds the frequency control word

K at every clock cycle fs. The accumulator output points

to a location in the Table ROM/RAM. The DAC

converts the digital data into an analog waveform. The

LPF filters out the clock frequency to provide a pure

waveform.

SFG-2000 Series User Manual

12

Lineup/Features

Series lineup

Features

Lineup

Duty

cycle

Offset

TTL/

CMOS

Sweep AM/

FM

Counter

SFG-2004 (4MHz)

●

●

●

―

―

―

SFG-2007 (7MHz)

●

●

●

―

―

―

SFG-2010 (10MHz)

●

●

●

―

―

―

SFG-2020 (20MHz)

●

●

●

―

―

―

SFG-2104 (4MHz)

●

●

●

●

●

●

SFG-2107 (7MHz)

●

●

●

●

●

●

SFG-2110 (10MHz)

●

●

●

●

●

●

SFG-2120 (20MHz)

●

●

●

●

●

●

Main features

Performance

•

High resolution using DDS and FPGA technology

•

High frequency accuracy: 20ppm

•

Low distortion: −55dBc

•

High resolution 100mHz maintained at full range

Features

•

Wide output frequency range: 4, 7, 10, 20MHz

•

Various output waveforms: Sine, Square, and Triangle

•

TTL/CMOS output

•

Variable DC offset control

•

Output overload protection

•

Store/recall: 10 settings

•

Counter up to 150MHz high frequency (SFG-2100

series)

•

AM/FM with internal and external (SFG-2100 series)

•

Sweep mode with LINE and LOG (SFG-2100 series)

Input/Output

Terminals

•

Frequency output

•

TTL/CMOS output

•

Counter input (SFG-2100 series)

•

External modulation input (SFG-2100 series)