Data sheet – GE Industrial Solutions CP2725AC54TE User Manual

Page 10

GE

Data Sheet

CP2725AC54TE CPL High Efficiency Rectifier

100-120/200-277V

AC

input; Default Outputs: ±54V

DC

@ 2725W, 5V

DC

@ 4W

January 30, 2014

©2013 General Electric Company. All rights reserved.

Page 10

Status Signals

Power Capacity:

A HI on this pin indicates that the rectifier

delivers high line rated output power; a LO indicates that the

rectifier is connected to low line configured for 1200W

operation.

Power Fail Warning:

This signal is HI when the main output is

being delivered and goes LO for the duration listed in this data

sheet prior to the output decaying below the listed voltage

level.

Fault:

This signal goes LO for any failure that requires rectifier

replacement. These faults may be due to:

Fan failure

Over-temperature warning

Over-temperature shutdown

Over-voltage shutdown

Internal Rectifier Fault

Digital Feature Descriptions

PMBus™ compliance:

The power supply is fully compliant to

the Power Management Bus (PMBus™) rev1.2 requirements

with the following exceptions:

The power supply continuously updates its STATUS and ALARM

registers to the latest state in order to capture the ‘present’

state of the power supply. There are a number of indicators,

such as those indicating a communications fault (PEC error,

data error) that do not get cleared until specifically instructed

by the host controller sending a clear_faults command. A ‘bit’

indicator notifies the user if the STATUS and ALARM registers

changed since the last ‘read’ by the host controller.

For example, if a voltage surge causes a momentary shutdown

for over voltage the power supply will automatically restart if

the ‘auto_restart’ feature is invoked. During the momentary

shutdown the power supply issues an Alert# indicating to the

system controller that a status change has occurred. If the

system controller reads back the STATUS and ALARM registers

while the power supply is shut down it will get the correct fault

condition. However, inquiry of the state of the power supply

after the restart event would indicate that the power supply is

functioning correctly. The STATUS and ALARM indicators did

not freeze at the original shutdown state and so the reason for

the original Alert# is erased. The restart ‘bit’ would be set to

indicate that an event has occurred.

The power supply also clears the STATUS and ALARM registers

after a successful read back of the information in these

registers, with the exception of communications error alarms.

This automated process improves communications efficiency

since the host controller does not have to issue another

clear_faults command to clear these registers.

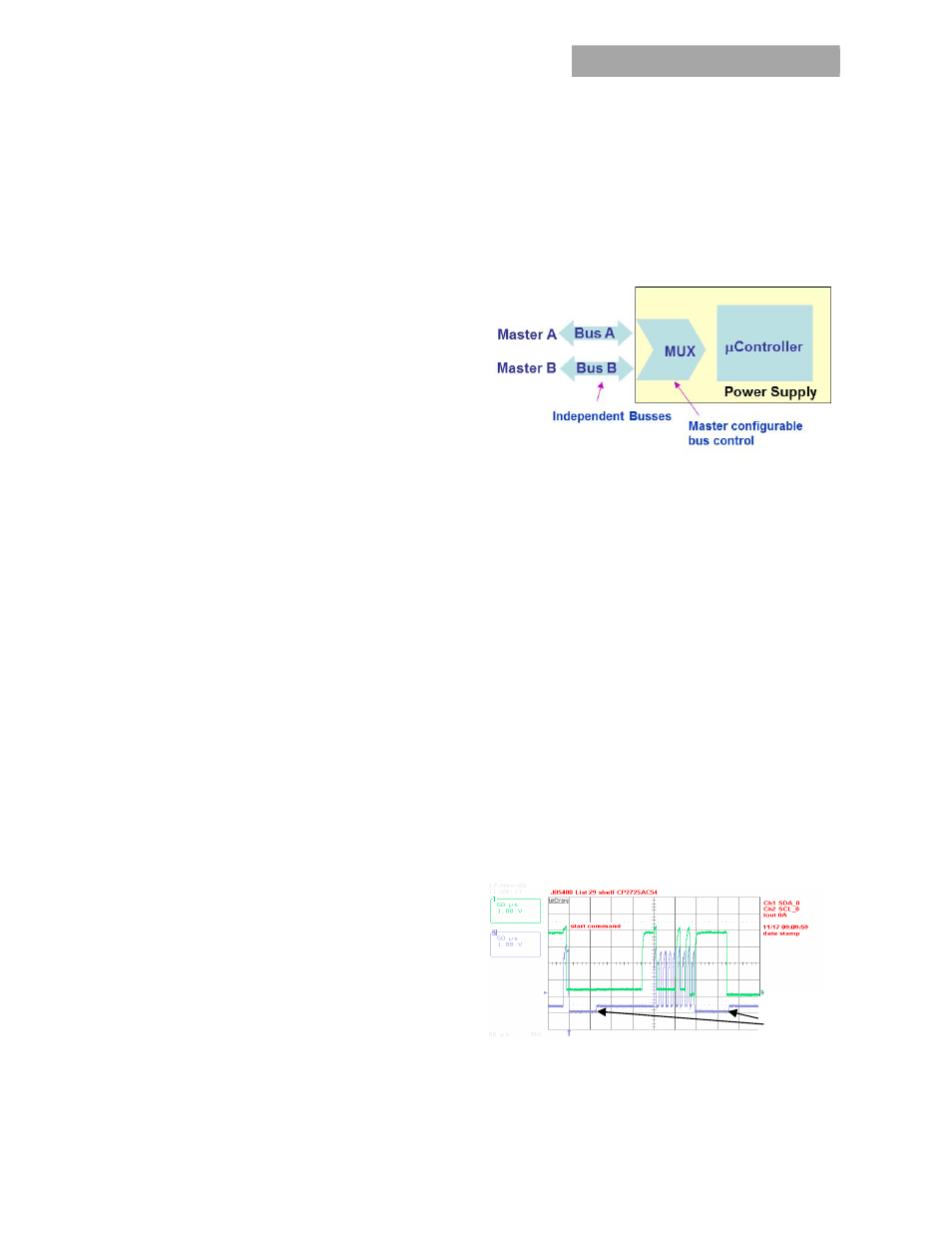

Dual, redundant buses:

Two independent I

2

C lines provide

true communications bus redundancy and allow two

independent controllers to sequentially control the power

supply. For example, a short or an open connection in one of

the I

2

C lines does not affect communications capability on the

other I

2

C line. Failure of a ‘master’ controller does not affect the

power supplies and the second ‘master’ can take over control

at any time.

Using the PCA9541 multiplexer:

Transition between the two

I

2

C lines is provided by the industry standard PCA9541 I

2

C

master selector multiplexer. Option 01 of the device code is

supplied which, upon start-up, connects channel 0 to the

power supply. In this fashion applications using only a single

I

2

C line can immediately start talking across the bus without

first requiring to reconfigure the multiplexer.

Figure 14. Diagram showing conceptual representation

of the dual I

2

C bus system.

Control can be taken over at any time by a specific ‘master’

even during data transmission to the other ‘master’. The

‘master’ needs to be able to handle incomplete transmissions

in the multi-master environment in case switching should

commence in the middle of data transmission.

Master/Slave:

The ‘host controller’ is always the MASTER.

Power supplies are always SLAVES. SLAVES cannot initiate

communications or toggle the Clock. SLAVES also must

respond expeditiously at the command of the MASTER as

required by the clock pulses generated by the MASTER.

Clock stretching:

The ‘slave’ µController inside the power

supply may initiate clock stretching if it is busy and it desires to

delay the initiation of any further communications. During the

clock stretch the ‘slave’ may keep the clock LO until it is ready

to receive further instructions from the host controller. The

maximum clock stretch interval is 25ms.

The host controller needs to recognize this clock stretching,

and refrain from issuing the next clock signal, until the clock

line is released, or it needs to delay the next clock pulse

beyond the clock stretch interval of the power supply.

Note that clock stretching can only be performed after

completion of transmission of the 9

th

ACK bit, the exception

being the START command.

Figure 14. Example waveforms showing clock stretching.

Communications speed:

Both 100kHz and 400kHz clock rates

are supported. The power supplies default to the 100kHz clock

rate.

Clock

Stretch