Rainbow Electronics BR24L02FVM-W User Manual

Page 8

BR24L02-W / BR24L02F-W / BR24L02FJ-W /

Memory ICs

BR24L02FV-W / BR24L02FVM-W

8/25

zDevice operation

1) Start condition (Recognition of start bit)

•

All commands are proceeded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH.

•

The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command

until this condition has been met. (See Fig.4 SYNCHRONOUS DATA TIMING)

2) Stop condition (Recognition of stop bit)

•

All communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is

HIGH. (See Fig.4 SYNCHRONOUS DATA TIMING)

3) Notice about write command

•

In the case that stop condition is not executed in WRITE mode, transferred data will not be written in a memory.

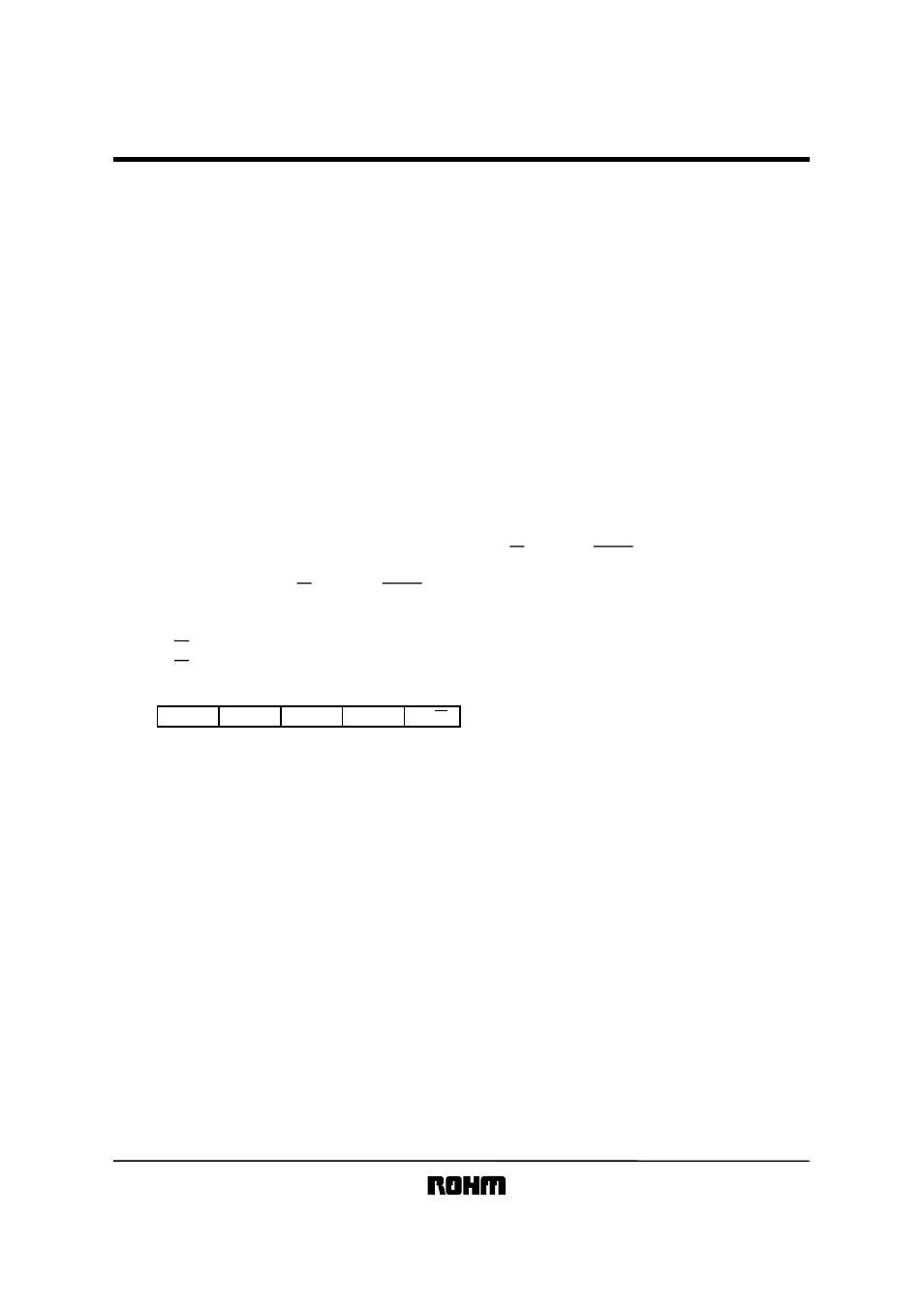

4) Device addressing

•

Following a START condition, the master output the slave address to be accessed.

•

The most significant four bits of the slave address are the “device type identifier”, for this device it is fixed as “1010”.

•

The next three bit (device address) identify the specified device on the bus.

The device address is defined by the state of A0, A1 and A2 input pins. This IC works only when the device address

inputted from SDA pin correspond to the state of A0, A1 and A2 input pins. Using this address scheme, up to eight

device may be connected to the bus. The last bit of the stream (R/W - - - READ / WRITE) determines the operation to

the performed.

•

The last bit of the stream (R/W - - - READ / WRITE) determines the operation to be performed. When set to “1”, a read

operation is selected ; when set to “0”, a write operation is selected.

R / W set to “0” - - - - - - WRITE (including word address input of Random Read)

R / W set to “1” - - - - - - READ

A2

A1

A0

1010

R / W

5) Write protect (WP)

When WP pin set to V

CC

(H level), write protect is set for 256 words (all address).

When WP pin set to GND (L level), enable to write 256 words (all address).

Either control this pin or connect to GND (or V

CC

). It is inhibited from being left unconnected.