Rainbow Electronics BR24L02FVM-W User Manual

Page 13

BR24L02-W / BR24L02F-W / BR24L02FJ-W /

Memory ICs

BR24L02FV-W / BR24L02FVM-W

13/25

zApplication

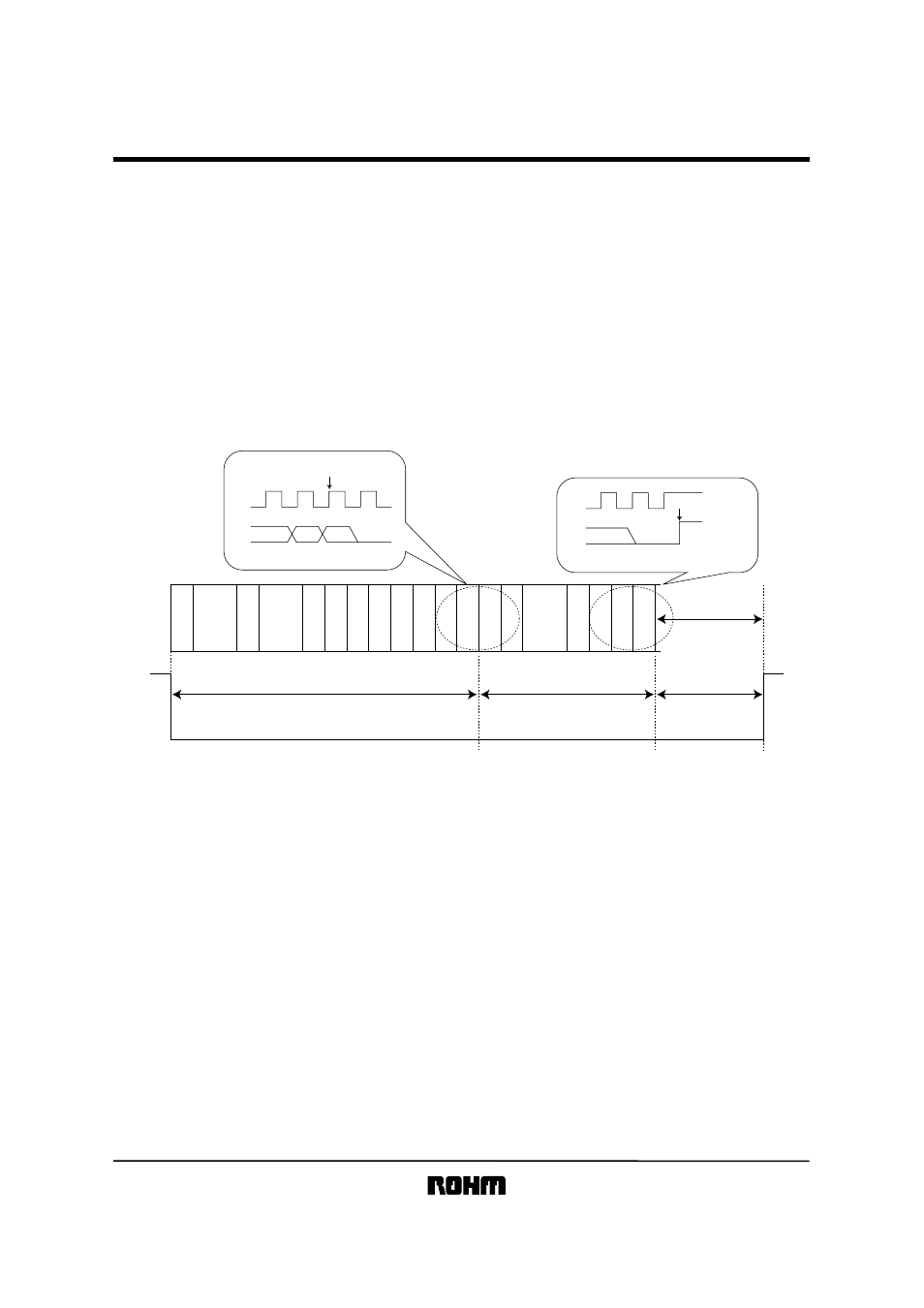

1) WP effective timing

WP is fixed to “H” or “L” usually. But in case of controlling WP to cancel the write command, please pay attention to

[

WP effective timing

]

as follows.

During write command input, write command is canceled by controlling WP “H” within the WP cancellation effective

period.

The period from the start condition to the rising edge of the clock which take in D0 of the data (the first byte of the data

for Page Write) is the cancellation invalid period. WP input is don’t care during the period. Setup time for rising edge of

the SCL which takes in D0 must be more than 100ns.

The period from the rising edge of SCL which takes in D0 to the end of internal write cycle (t

WR

) is the cancellation

effective period. In case of setting WP to “H” during t

WR

, WRITE operation is stopped in the middle and the data of

accessing address is not guaranteed, so that write correct data again please.

It is not necessary waiting t

WR

(5msmax.) after stopping command by WP, because the device is stand by state.

S

T

A

R

T

A

C

K

L

A

C

K

L

A

C

K

L

A

C

K

L

A

C

K

L

S

T

O

P

SLAVE

ADDRESS

WORD

ADDRESS

DATA

D7

D6

D5

D4

D3

D2

D1

D0

SDA

WP

tWR

WP cancellation invalid period

WP cancellation effective period

No data will be written

Stop of the write

operation

Data is not

guaranteed

SCL

SDA

D1

D0

ACK

AN ENLARGEMENT

· The rising edge of the clock

which take in D0

SCL

SDA

D0

ACK

AN ENLARGEMENT

· The rising edge

of SDA

Fig.13 WP EFFECTIVE TIMING