Rainbow Electronics BR24L02FVM-W User Manual

Page 18

BR24L02-W / BR24L02F-W / BR24L02FJ-W /

Memory ICs

BR24L02FV-W / BR24L02FVM-W

18/25

•

LV

CC

circuit

LV

CC

circuit inhibit write operation at low voltage, and prevent an inadvertent write. Below the LV

CC

voltage

(Typ.=1.2V), write operation is inhibited.

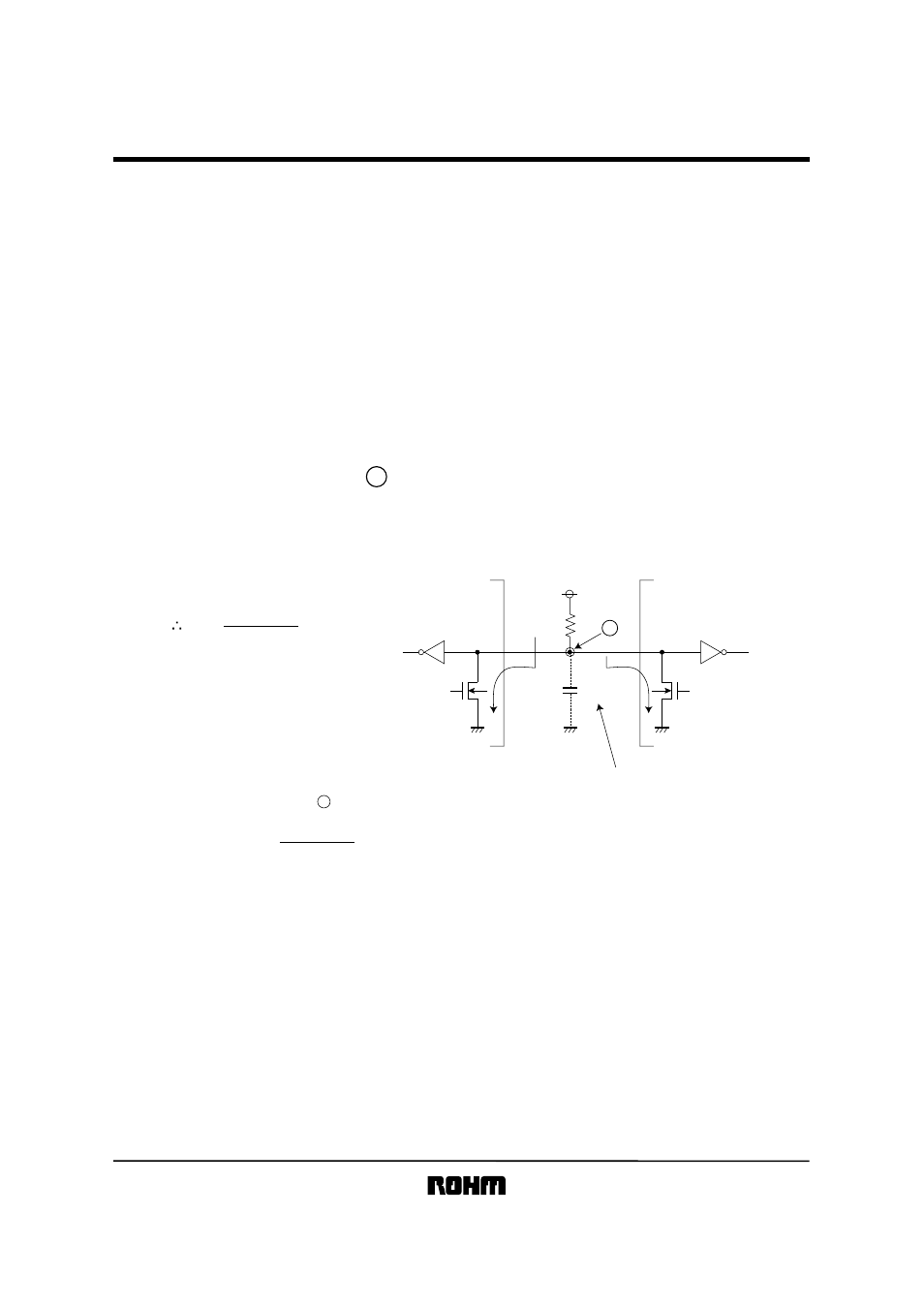

6) I / O circuit

•

Pull up resister of SDA pin

The pull up resister is needed because SDA is NMOS open drain. Decide the value of this resister (R

PU

) properly,

by considering V

IL

, I

L

characteristics of a controller which control the device and V

OH

, I

OL

characteristics of the device.

If large R

PU

is chosen, clock frequency need to be slow. In case of small R

PU

, the operating current increases.

•

Maximum of R

PU

Maximum of R

PU

is determined by following factor.

① SDA rise time determined by R

PU

and the capacitance of bus line (CBUS) must be less than T

R

.

And the other timing must keep the conditions of AC spec.

② When SDA bus is HIGH, the voltage A of SDA bus determined by a total input leak (I

L

) of the all devices

connected

to the bus and R

PU

must be enough higher than input HIGH level of a controller and the device,

including noise margin 0.2 V

CC

.

A

IL

IL

MICRO

COMPUTER

BR24LXX

SDA PIN

R

PU

THE CAPACITANCE OF

BUS LINE (CBUS)

V

CC

−

I

L

R

PU

−

0.2V

CC

≥

V

IH

R

PU

≤

0.8V

CC

−

V

IH

IL

R

PU

≤

0.8

Ч

3

−

0.7

Ч

3

10

Ч

10

−

6

≤

300 [k

Ω

]

Examples : When V

CC

=

3V I

L

=

10

µ

A V

IH

=

0.7V

CC

According to 2