Memory array – Rainbow Electronics AT45DQ321 User Manual

Page 6

6

AT45DQ321 [ADVANCE DATASHEET]

DS-45DQ321-031–DFLASH–12/2012

3.

Memory Array

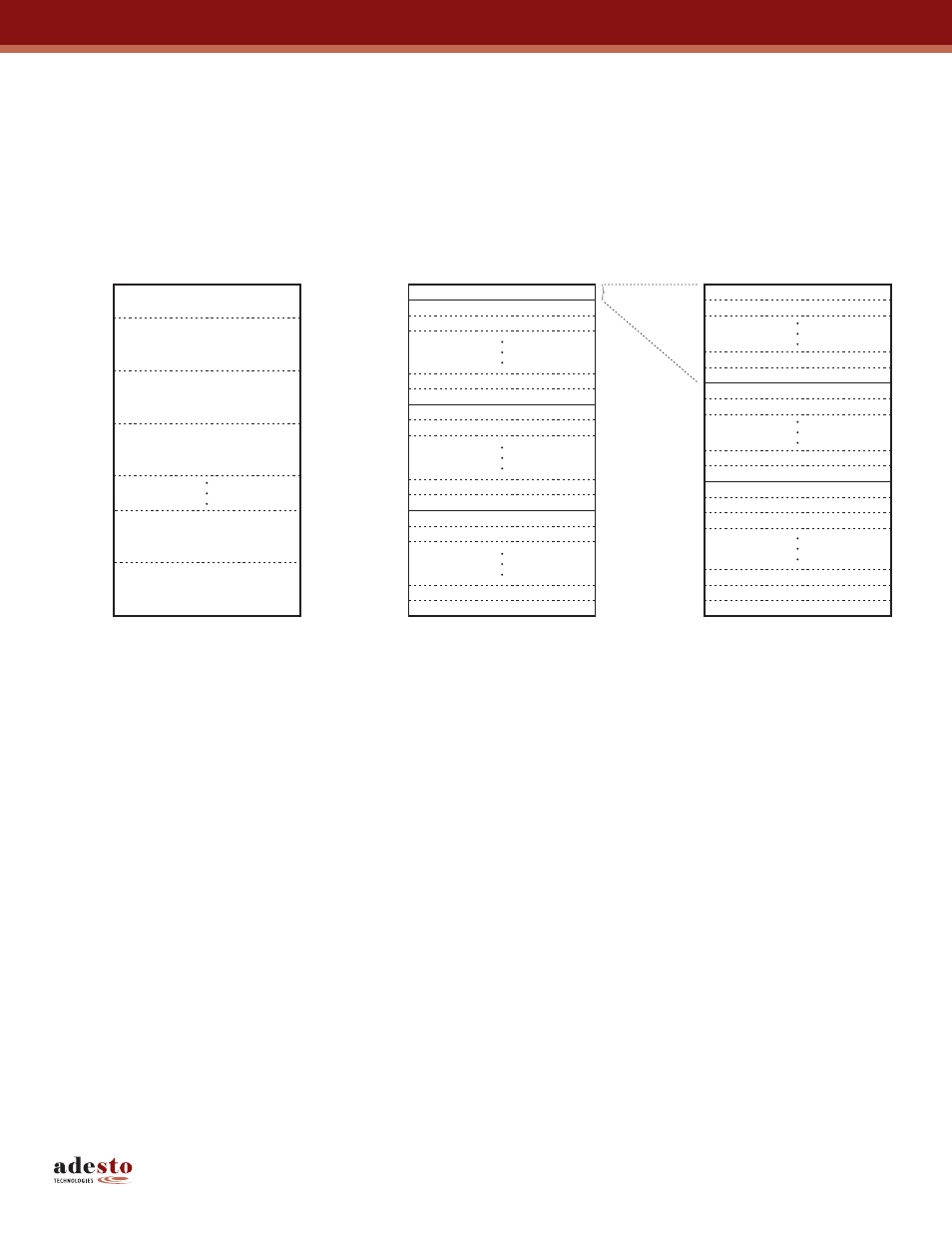

To provide optimal flexibility, the AT45DQ321 memory array is divided into three levels of granularity comprising of

sectors, blocks, and pages.

Figure 3-1, Memory Architecture Diagram

illustrates the breakdown of each level and details

the number of pages per sector and block. Program operations to the DataFlash can be done at the full page level or at

the byte level (a variable number of bytes). The erase operations can be performed at the chip, sector, block, or page

level.

Figure 3-1. Memory Architecture Diagram

Sector 0a = 8 pages

4,096/4,224 bytes

Sector 0b = 120 pages

61,440/63,360 bytes

Block = 4,096/4,224 bytes

8 Pages

Sector 0a

Sector 0b

Page = 512/528 bytes

Page 0

Page 1

Page 6

Page 7

Page 8

Page 9

Page 8,190

Page 8,191

Block 0

Page 14

Page 15

Page 16

Page 17

Page 18

Block 1

Sector Architecture

Block Architecture

Page Architecture

Block 0

Block 1

Block 30

Block 31

Block 32

Block 33

Block 1022

Block 1023

Block 62

Block 63

Block 64

Block 65

Sector 1

Sector 63 = 128 pages

65,536/67,584 bytes

Block 2

Sector 1 = 128 pages

65,536/67,584 bytes

Sector 62 = 128 pages

65,536/67,584 bytes

Sector 2 = 128 pages

65,536/67,584 bytes