2 quad disable command – Rainbow Electronics AT45DQ321 User Manual

Page 37

37

AT45DQ321 [ADVANCE DATASHEET]

DS-45DQ321-031–DFLASH–12/2012

9.6.2

Quad Disable Command

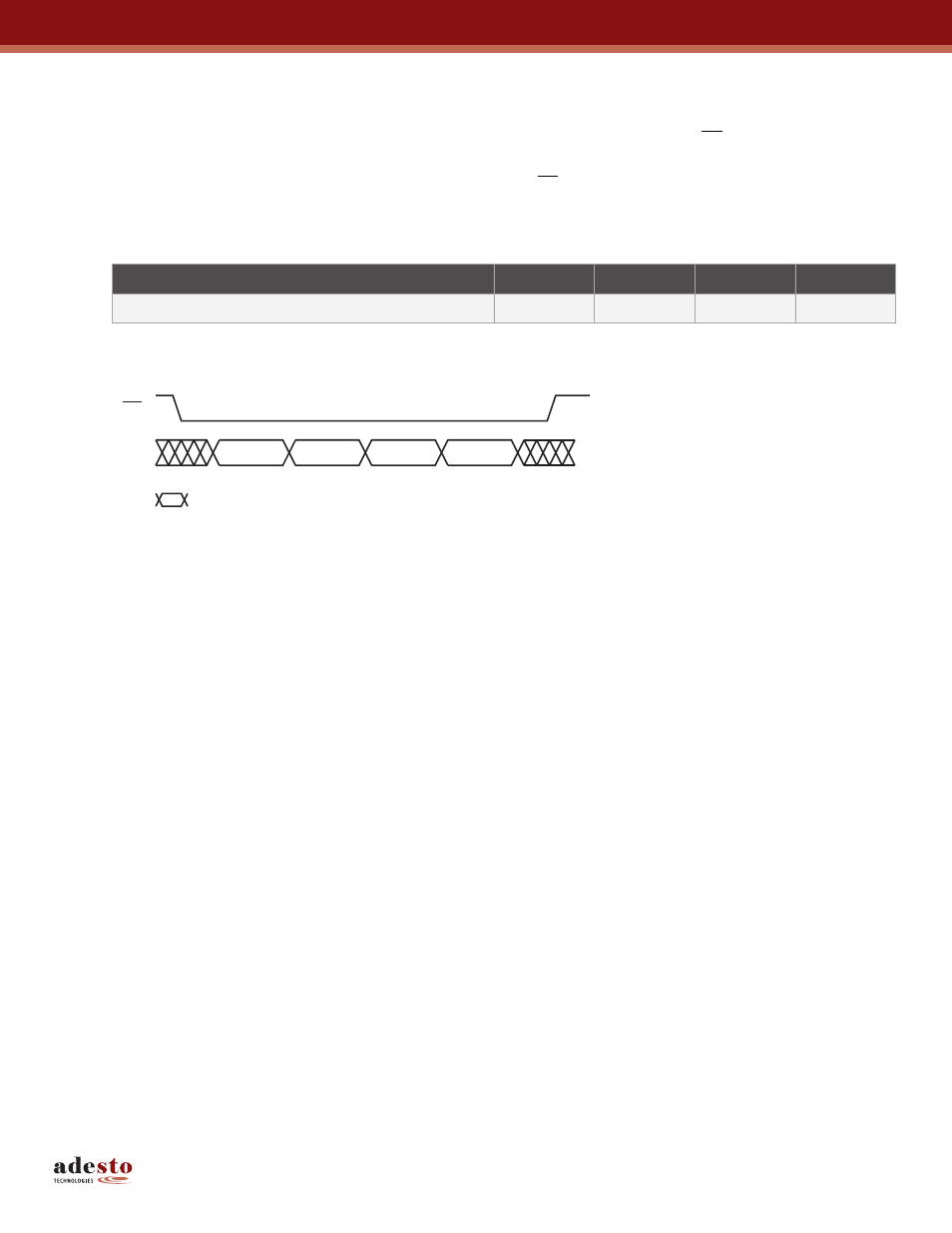

The Quad Disable command is used to program the QE bit of the non-volatile Configuration Register to a Logical 0 to

disable the Quad I/O functionality of the device. To issue the Quad Disable command, the CS pin must first be asserted

followed by a four byte opcode of 3Dh, 2Ah, 81h and 67h.

After the last bit of the four byte opcode has been clocked in, the CS pin must be deasserted allowing the QE bit of the

Configuration Register to be modified within the time of t

WRCR

.

Table 9-4.

Quad Disable Command

Figure 9-4. Quad Disable

Command

Byte 1

Byte 2

Byte 3

Byte 4

Quad Disable

3Dh

2Ah

81h

67h

3Dh

2Ah

81h

67h

CS

SI

Each transition represents eight bits

See also other documents in the category Rainbow Electronics Storage:

- W27E010 (14 pages)

- W27L520 (16 pages)

- W29EE512 (21 pages)

- W27E512 (16 pages)

- W24100 (11 pages)

- W27E040 (15 pages)

- W25Q32 (60 pages)

- W49L102 (21 pages)

- W29C040 (20 pages)

- W29EE011 (20 pages)

- W49F020 (21 pages)

- W2465 (10 pages)

- W24256 (10 pages)

- W982516CH (43 pages)

- MAX16014 (12 pages)

- W24512A (10 pages)

- W27E020 (14 pages)

- W29C020C (21 pages)

- W25X64 (47 pages)

- W24257 (11 pages)

- W24L257 (10 pages)

- W9864G2GH (48 pages)

- W24L11 (11 pages)

- W27L010 (14 pages)

- W27E520 (16 pages)

- W27LE520 (16 pages)

- W9825G6CH (43 pages)

- W49F002U (23 pages)

- W9864G6GB (47 pages)

- AT45DB011B (32 pages)

- AT45DB642 (71 pages)

- AT45DB642 (37 pages)

- AT45DB161D (51 pages)

- AT27LV040A (12 pages)

- AT29LV010A (15 pages)

- HT24LC08 (11 pages)

- AT29C257 (12 pages)

- AT45DB161B (32 pages)

- AT27C1024 (12 pages)

- AT28BV256 (12 pages)

- AT28C040 (12 pages)

- DS1258Y_AB (9 pages)

- AT28BV64B (12 pages)

- AT27C512R (12 pages)

- DS1220AB_AD (9 pages)