Port a as general digital i/o, Port a schematics – Rainbow Electronics AT90LS8535 User Manual

Page 77

77

AT90S/LS8535

1041H–11/01

Port A as General Digital I/O

All eight pins in Port A have equal functionality when used as digital I/O pins.

PAn, general I/O pin: The DDAn bit in the DDRA register selects the direction of this pin.

If DDAn is set (one), PAn is configured as an output pin. If DDAn is cleared (zero), PAn

is configured as an input pin. If PORTAn is set (one) when the pin is configured as an

input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the

PORTAn has to be cleared (zero) or the pin has to be configured as an output pin.The

port pins are tri-stated when a reset condition becomes active, even if the clock is not

running.

Note:

n: 7,6…0, pin number.

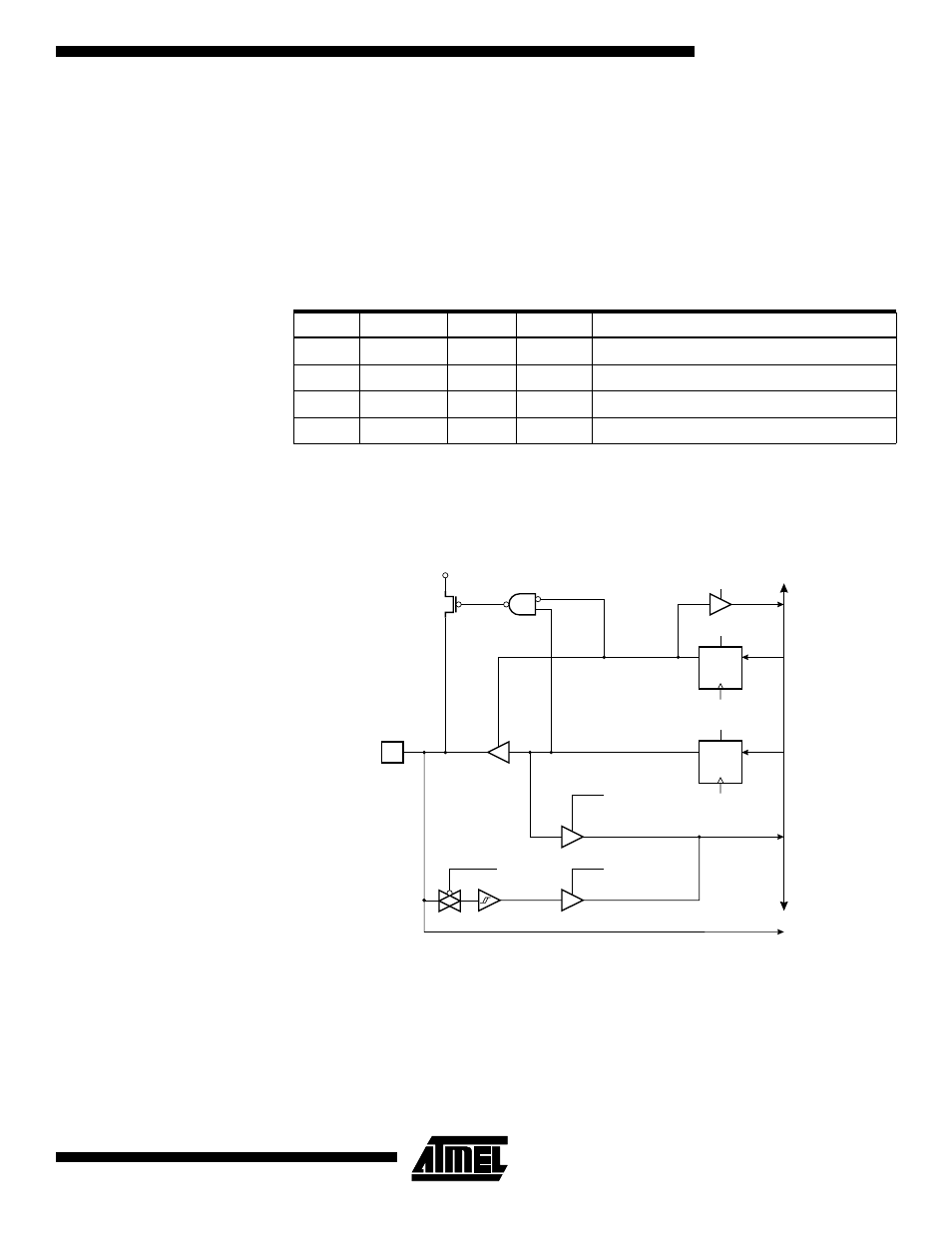

Port A Schematics

Note that all port pins are synchronized. The synchronization latch is, however, not

shown in the figure.

Figure 51. Port A Schematic Diagrams (Pins PA0 - PA7)

Table 29. DDAn Effects on Port A Pins

DDAn

PORTAn

I/O

Pull-up

Comment

0

0

Input

No

Tri-state (high-Z)

0

1

Input

Yes

PAn will source current if ext. pulled low

1

0

Output

No

Push-pull Zero Output

1

1

Output

No

Push-pull One Output

DA

T

A

BUS

D

D

Q

Q

RESET

RESET

C

C

WD

WP

RD

MOS

PULL-

UP

PAn

ADCn

TO ADC MUX

WP:

WD:

RL:

RP:

RD:

n:

WRITE PORTA

WRITE DDRA

READ PORTA LATCH

READ PORTA PIN

READ DDRA

0-7

DDAn

PORTAn

RL

RP

PWRDN