Watchdog timer, Watchdog timer control register – wdtcr – Rainbow Electronics AT90LS8535 User Manual

Page 49

49

AT90S/LS8535

1041H–11/01

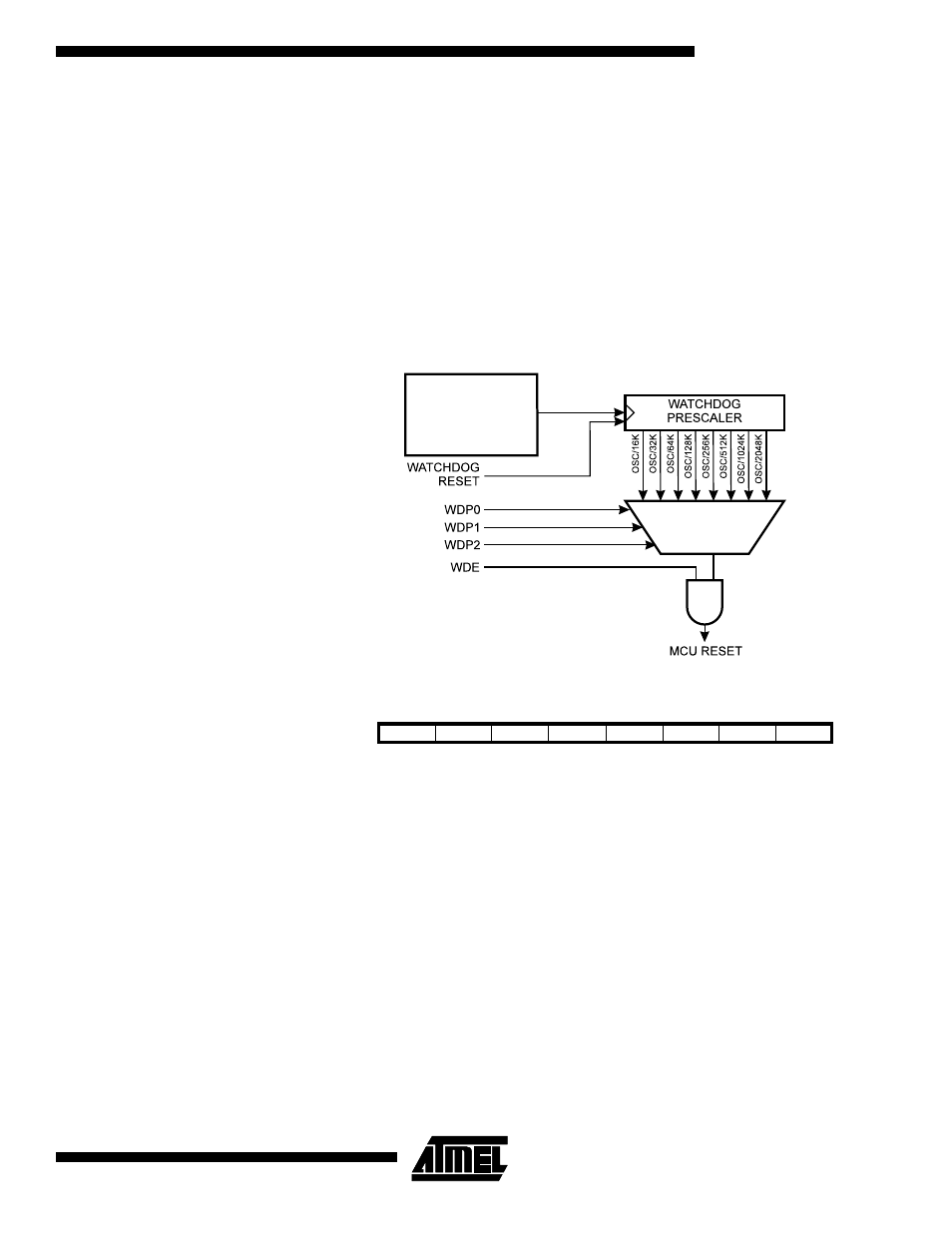

Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip oscillator. By controlling the

Watchdog Timer prescaler, the Watchdog reset interval can be adjusted as shown in

Table 21. See characterization data for typical values at other V

CC

levels. The WDR

(Watchdog Reset) instruction resets the Watchdog Timer. Eight different clock cycle

periods can be selected to determine the reset period. If the reset period expires without

another Watchdog reset, the AT90S8535 resets and executes from the reset vector. For

timing details on the Watchdog reset, refer to page 22.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be

followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer

Control Register for details.

Figure 36. Watchdog Timer

Watchdog Timer Control

Register – WDTCR

• Bits 7..5 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

• Bit 4 – WDTOE: Watchdog Turn-off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the Watchdog will

not be disabled. Once set, hardware will clear this bit to zero after four clock cycles.

Refer to the description of the WDE bit for a Watchdog disable procedure.

• Bit 3 – WDE: Watchdog Enable

When the WDE is set (one) the Watchdog Timer is enabled and if the WDE is cleared

(zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE

bit is set (one). To disable an enabled Watchdog Timer, the following procedure must be

followed:

1 MHz at V

CC

= 5V

350 kHz at V

CC

= 3V

Oscillator

Bit

7

6

5

4

3

2

1

0

$21 ($41)

–

–

–

WDTOE

WDE

WDP2

WDP1

WDP0

WDTCR

Read/Write

R

R

R

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0