Bit timer/counter1 – Rainbow Electronics AT90LS8535 User Manual

Page 35

35

AT90S/LS8535

1041H–11/01

16-bit Timer/Counter1

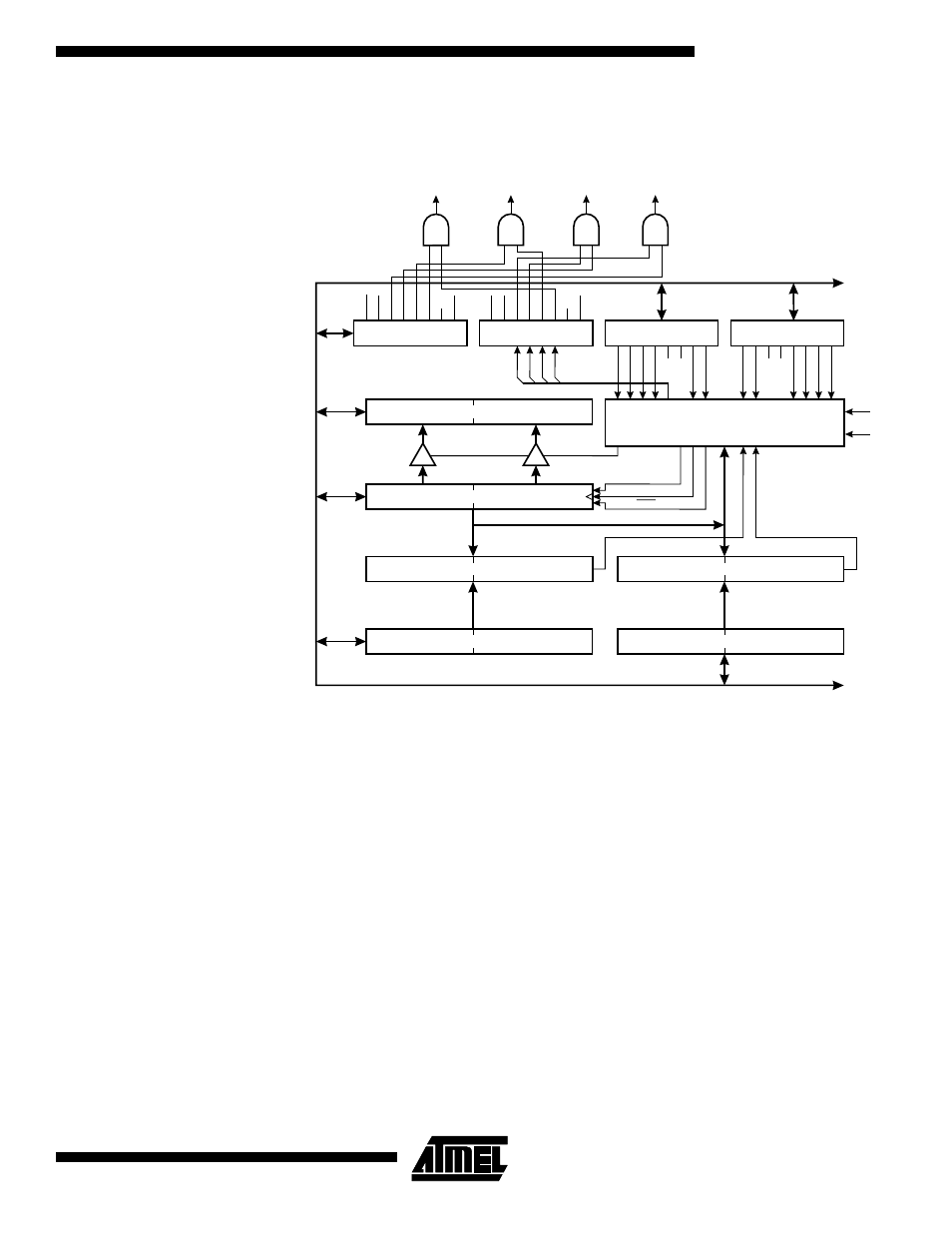

Figure 31 shows the block diagram for Timer/Counter1.

Figure 31. Timer/Counter1 Block Diagram

The 16-bit Timer/Counter1 can select clock source from CK, prescaled CK or an exter-

nal pin. In addition, it can be stopped as described in the specification for the

Timer/Counter1 Control Registers (TCCR1A and TCCR1B). The different status flags

(Overflow, Compare Match and Capture Event) and control signals are found in the

Timer/Counter1 Control Registers (TCCR1A and TCCR1B). The interrupt enable/dis-

able settings for Timer/Counter1 are found in the Timer/Counter Interrupt Mask Register

(TIMSK).

When Timer/Counter1 is externally clocked, the external signal is synchronized with the

oscillator frequency of the CPU. To assure proper sampling of the external clock, the

minimum time between two external clock transitions must be at least one internal CPU

clock period. The external clock signal is sampled on the rising edge of the internal CPU

clock.

The 16-bit Timer/Counter1 features both a high-resolution and a high-accuracy usage

with the lower prescaling opportunities. Similarly, the high prescaling opportunities

makes the Timer/Counter1 useful for lower speed functions or exact timing functions

with infrequent actions.

The Timer/Counter1 supports two Output Compare functions using the Output Compare

Register 1A and B (OCR1A and OCR1B) as the data sources to be compared to the

Timer/Counter1 contents. The Output Compare functions include optional clearing of

8-BIT D

A

TA

B

U

S

T/C1 CONTROL

REGISTER B (TCCR1B)

T/C1 CONTROL

REGISTER A (TCCR1A)

T/C1 INPUT CAPTURE REGISTER (ICR1)

16 BIT COMPARATOR

16 BIT COMPARATOR

TIMER/COUNTER1 OUTPUT COMPARE REGISTER A

TIMER/COUNTER1 OUTPUT COMPARE REGISTER B

TIMER/COUNTER1 (TCNT1)

TIMER INT. FLAG

REGISTER (TIFR)

0

0

0

0

0

0

7

7

7

7

7

7

8

8

8

8

8

8

15

15

15

15

15

15

CONTROL

LOGIC

COM1A1

COM1B1

CS12

TO

V

1

TO

V

1

TO

V

0

OCF1A

OCF1A

OCF1B

OCF1B

ICF1

ICF1

COM1A0

COM1B0

CS1

1

CTC1

PWM1

1

PWM10

ICES1

ICNC1

CS10

CK

T/C1 COMPARE

MATCHA IRQ

T/C1 COMPARE

MATCHB IRQ

T/C1 INPUT

CAPTURE IRQ

T/C1 OVER-

FLOW IRQ

CAPTURE

TRIGGER

T/C CLOCK SOURCE

T/C CLEAR

UP/DOWN

TIMER INT. MASK

REGISTER (TIMSK)

T

OIE0

T

OIE1

OCIE1A

OCIE1B

TICIE1

T

OIE2

TO

V

2

OCIE2

OCF2

T1