Timer/counter2 control register – tccr2 – Rainbow Electronics AT90LS8535 User Manual

Page 43

43

AT90S/LS8535

1041H–11/01

Timer/Counter Control Register (TCCR2). The interrupt enable/disable settings are

found in the Timer/Counter Interrupt Mask Register (TIMSK).

This module features a high-resolution and a high-accuracy usage with the lower pres-

caling opportunities. Similarly, the high prescaling opportunities make this unit useful for

lower speed functions or exact timing functions with infrequent actions.

The Timer/Counter supports an Output Compare function using the Output Compare

Register (OCR2) as the data source to be compared to the Timer/Counter contents.The

Output Compare function includes optional clearing of the counter on compare match

and action on the Output Compare Pin, PD7(OC2), on compare match. Writing to

PORTD7 does not set the OC2 value to a predetermined value.

Timer/Counter2 can also be used as an 8-bit Pulse Width Modulator. In this mode,

Timer/Counter2 and the Output Compare Register serve as a glitch-free, stand-alone

PWM with centered pulses. Refer to page 45 for a detailed description of this function.

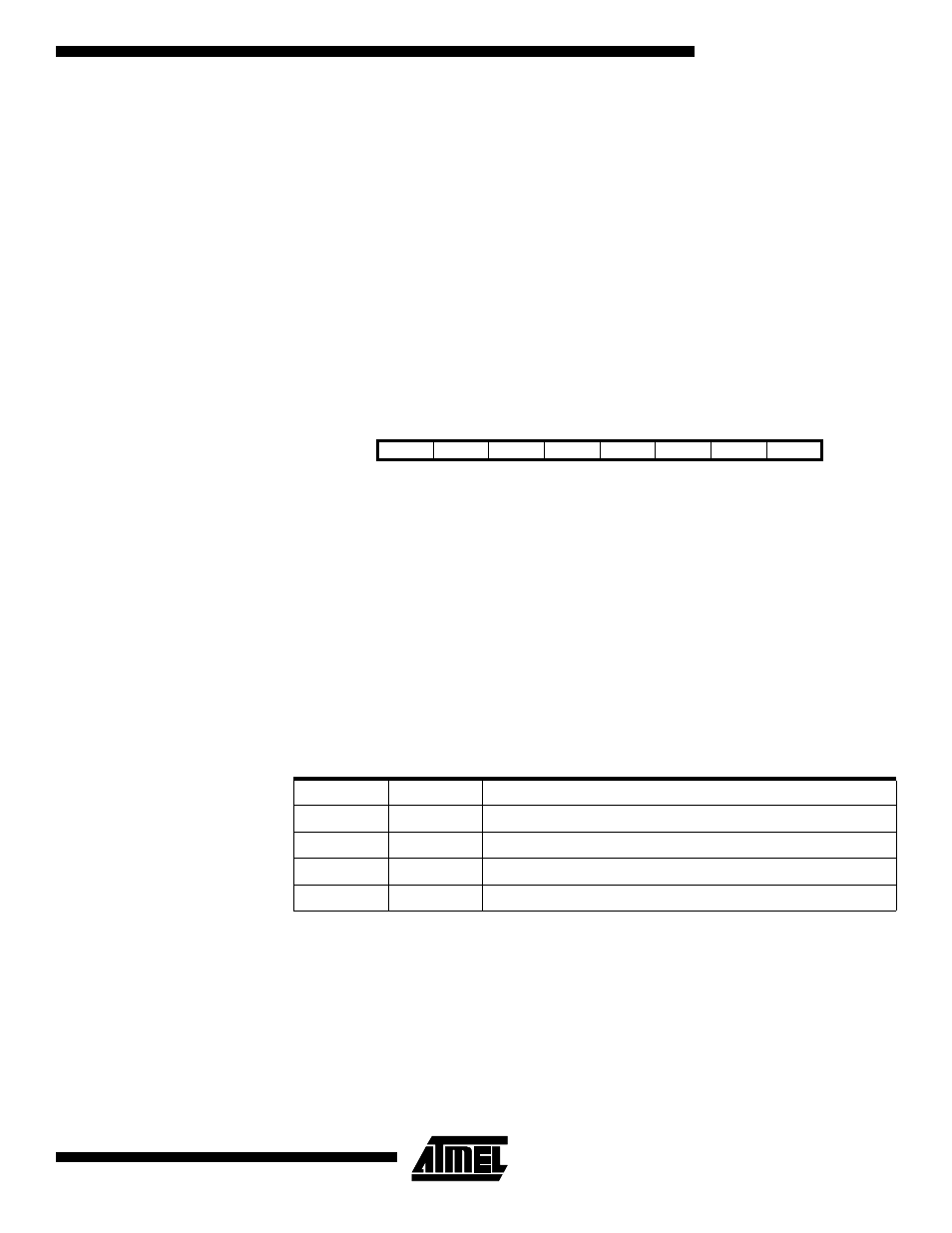

Timer/Counter2 Control

Register – TCCR2

• Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8535 and always reads as zero.

• Bit 6 – PWM2: Pulse Width Modulator Enable

When set (one), this bit enables PWM mode for Timer/Counter2. This mode is described

on page 45.

• Bits 5, 4 – COM21, COM20: Compare Output Mode, Bits 1 and 0

The COM21 and COM20 control bits determine any output pin action following a com-

pare match in Timer/Counter2. Output pin actions affect pin PD7(OC2). This is an

alternative function to an I/O port and the corresponding direction control bit must be set

(one) to control an output pin. The control configuration is shown in Table 17.

Note:

In PWM mode, these bits have a different function. Refer to Table 19 for a detailed

description.

• Bit 3 – CTC2: Clear Timer/Counter on Compare Match

When the CTC2 control bit is set (one), Timer/Counter2 is reset to $00 in the CPU clock

cycle after a compare match. If the control bit is cleared, Timer/Counter2 continues

counting and is unaffected by a compare match. Since the compare match is detected in

the CPU clock cycle following the match, this function will behave differently when a

prescaling higher than 1 is used for the timer. When a prescaling of 1 is used and the

compare2 register is set to C, the timer will count as follows if CTC2 is set:

... | C-2 | C-1 | C | 0 | 1 |...

Bit

7

6

5

4

3

2

1

0

$25 ($45)

–

PWM2

COM21

COM20

CTC2

CS22

CS21

CS20

TCCR2

Read/Write

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Table 17. Compare Mode Select

COM21

COM20

Description

0

0

Timer/Counter disconnected from output pin OC2

0

1

Toggle the OC2 output line.

1

0

Clear the OC2 output line (to zero).

1

1

Set the OC2 output line (to one).