Spi control register – spcr – Rainbow Electronics AT90LS8535 User Manual

Page 57

57

AT90S/LS8535

1041H–11/01

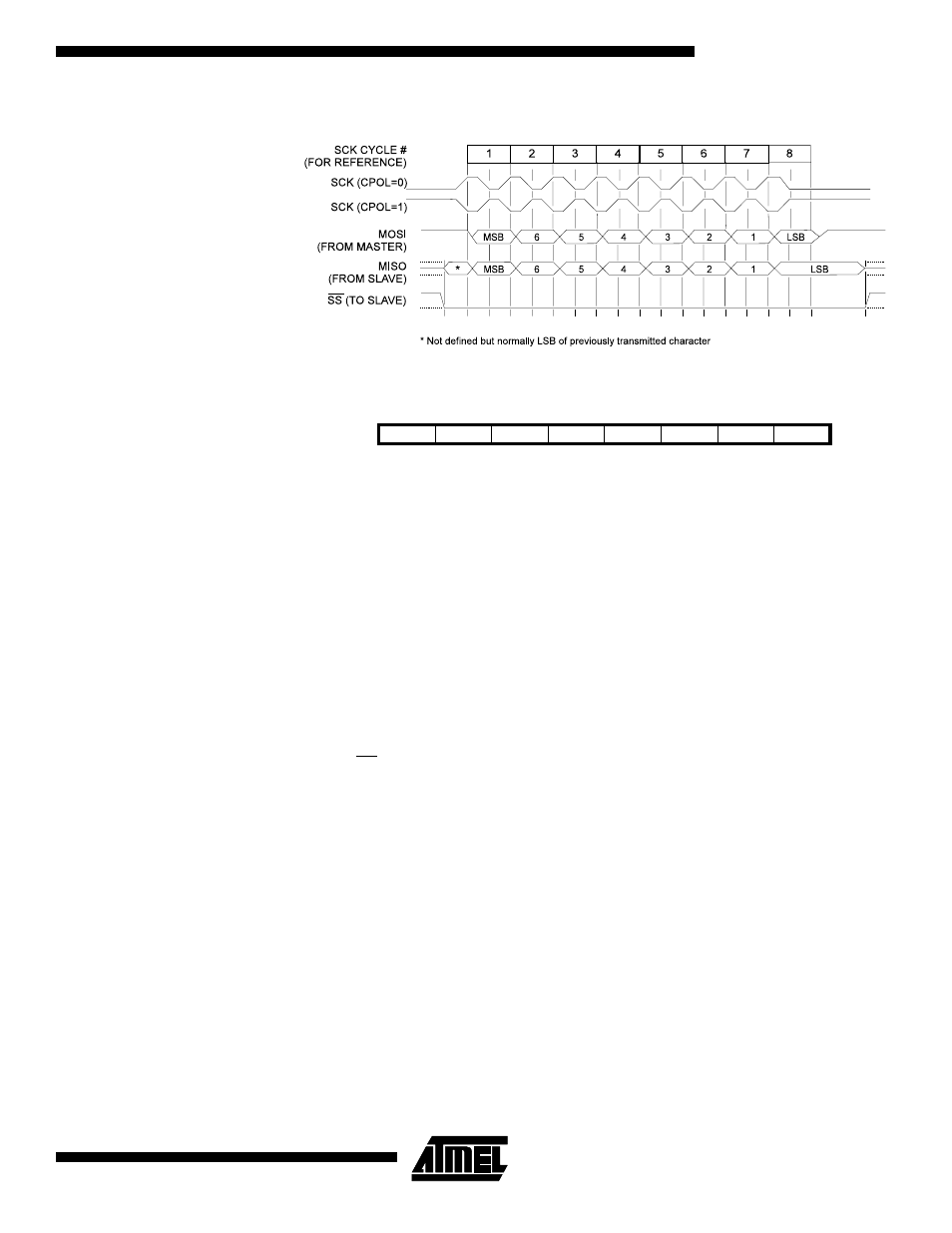

Figure 40. SPI Transfer Format with CPHA = 1 and DORD = 0

SPI Control Register – SPCR

• Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set

and the global interrupts are enabled.

• Bit 6 – SPE: SPI Enable

When the SPE bit is set (one), the SPI is enabled. This bit must be set to enable any SPI

operations.

• Bit 5 – DORD: Data Order

When the DORD bit is set (one), the LSB of the data word is transmitted first.

When the DORD bit is cleared (zero), the MSB of the data word is transmitted first.

• Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI Mode when set (one) and Slave SPI Mode when cleared

(zero). If SS is configured as an input and is driven low while MSTR is set, MSTR will be

cleared and SPIF in SPSR will become set. The user will then have to set MSTR to re-

enable SPI Master Mode.

• Bit 3 – CPOL: Clock Polarity

When this bit is set (one), SCK is high when idle. When CPOL is cleared (zero), SCK is

low when idle. Refer to Figure 39. and Figure 40. for additional information.

• Bit 2 – CPHA: Clock Phase

Refer to Figure 40 or Figure 41 for the functionality of this bit.

Bit

7

6

5

4

3

2

1

0

$0D ($2D)

SPIE

SPE

DORD

MSTR

CPOL

CPHA

SPR1

SPR0

SPCR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0